我要做24H製的時(shí)鐘~但我一直DEBUG~一直用不出來(lái)~

我Xilinx ISE 8.2i軟體~

請(qǐng)會(huì)的人幫我看一下哪出錯(cuò)了~謝

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity CLOCK_00_60 is

Port ( CLK : in STD_LOGIC;

RESET : in STD_LOGIC;

ENABLE : out STD_LOGIC_VECTOR (6 downto 0);

SEGMENT : out STD_LOGIC_VECTOR (6 downto 0));

end CLOCK_00_60;

architecture Behavioral of CLOCK_00_60 is

signal SCAN_CLK :STD_LOGIC;

signal COUNT_CLK :STD_LOGIC;

signal DECODE_BCD :STD_LOGIC_VECTOR (3 downto 0);

signal mineable :STD_LOGIC;

signal hreable :STD_LOGIC;

signal POSITION:STD_LOGIC_VECTOR (6 downto 0);

signal DIVIDER:STD_LOGIC_VECTOR (29 downto 1);

signal COUNT_BCD:STD_LOGIC_VECTOR (23 downto 0);

begin

-------------------------------------------------

process (CLK,RESET)

begin

if RESET = '0' then

DIVIDER <= ( others => '0');

elsif CLK' event and CLK = '1' then

DIVIDER <= DIVIDER + 1 ;

end if;

end process;

COUNT_CLK<=DIVIDER(24);

SCAN_CLK<=DIVIDER(15);

------------------------------------------------秒

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(3 downto 0)= x"9" then

COUNT_BCD(3 downto 0)<= x"0";

COUNT_BCD(7 downto 4)<= COUNT_BCD(7 downto 4)+1;

else

COUNT_BCD(3 downto 0)<= COUNT_BCD(3 downto 0)+1;

end if;

end if;

end process;

mineable <= '1' when COUNT_BCD(7 downto 0) = x"59" else '0';

----------------------------------------------------------分

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

if mineable = '1' then

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(11 downto 8)= x"9" then

COUNT_BCD(11 downto 8)<= x"0";

COUNT_BCD(15 downto 12)<= COUNT_BCD(15 downto 12)+1;

else

COUNT_BCD(11 downto 8)<= COUNT_BCD(11 downto 8)+1;

end if;

end if;

end if;

end process;

hreable <= '1' when COUNT_BCD(15 downto 8) = x"59" else '0';

-------------------------------------------------------------時(shí)

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

COUNT_BCD <= ( others => '0');

if mineable = '1' and hreable = '1' then

elsif SCAN_CLK' event and SCAN_CLK = '1' then

if COUNT_BCD(19 downto 16)= x"9" then

COUNT_BCD(19 downto 16)<= x"0";

COUNT_BCD(23 downto 20)<= COUNT_BCD(23 downto 20)+1;

if COUNT_BCD(19 downto 16)= x"2" then

COUNT_BCD(23 downto 20)<= x"0";

else

COUNT_BCD(19 downto 16)<= COUNT_BCD(19 downto 16)+1;

end if;

end if;

end if;

end if;

end process;

process(RESET,SCAN_CLK)

begin

if RESET = '0' then

POSITION <= "1111110";

elsif SCAN_CLK' event and SCAN_CLK = '1' then

POSITION<="111111"&POSITION(0);

end if;

end process;

ENABLE<=POSITION;

-----------------------------------------------------------

process(POSITION,SCAN_CLK)

begin

case POSITION is

when "1111110" => DECODE_BCD <=COUNT_BCD(3 downto 0); --秒

when "1111101" => DECODE_BCD <=COUNT_BCD(7 downto 4); --秒

when "1111011" => DECODE_BCD <=COUNT_BCD(11 downto 8); --分

when "1110111" => DECODE_BCD <=COUNT_BCD(15 downto 12); --分

when "1101111" => DECODE_BCD <=COUNT_BCD(19 downto 16); --時(shí)

when "1011111" => DECODE_BCD <=COUNT_BCD(23 downto 20); --時(shí)

when others => null;

end case;

end process;

with DECODE_BCD Select

SEGMENT<= "1000000" when X"0",

"1111001" when X"1",

"0100100" when X"2",

"0110000" when X"3",

"0011001" when X"4",

"0010010" when X"5",

"0000010" when X"6",

"1111000" when X"7",

"0000000" when X"8",

"0010000" when X"9",

"1111111" when others;

end Behavioral;

]]>

sbit LED=P1^1;

void Init_Timer0(void)

{

TMOD = 0x01;

TH0=0x3C; /* Init value */

TL0=0xB0;

EA=1; /* interupt enable */

ET0=1; /* enable timer0 interrupt */

TR0=1; }

main()

{

tt=0;

Init_Timer0();

do{

TH0=0x3C; /* Init value */

TL0=0xB0;

LED=~LED;

tt++;

if(tt==2000)

{

LED=~LED;

tt=0;

}//指示燈反相*/

}

while(!TF0);

為什么燈不能閃爍呢,是程序出問(wèn)題了么,問(wèn)題在什么地方,請(qǐng)高人指點(diǎn)一下,軟件仿真可以通過(guò),但是到實(shí)驗(yàn)板上就沒(méi)有燈閃爍,為什么呢]]>

一.大家不要盲目的報(bào)IT培訓(xùn)班,要先結(jié)合一下自己的興趣點(diǎn),看看自己到底是想成為一個(gè)什么樣的人,不要錯(cuò)誤的認(rèn)為自己是計(jì)算機(jī)系的同學(xué),被人家忽悠幾句,就有一種以后不做IT好像就埋沒(méi)了自己的天賦的那種感覺(jué)。要切記,與其從事一個(gè)自己根本不感興趣的行業(yè),不如回家老老實(shí)實(shí)呆著,想想自己究竟想成為什么樣的人來(lái)的實(shí)在。。。

二.確定了方向,決定自己要報(bào)這個(gè)培訓(xùn)班的時(shí)候,就要開(kāi)始選擇培訓(xùn)班了。選培訓(xùn)班這個(gè)事情,其實(shí)問(wèn)題很?chē)?yán)重,如果錯(cuò)選了,后果也很?chē)?yán)重。現(xiàn)在世面上有很多培訓(xùn)班,到底報(bào)哪個(gè)呢?因?yàn)槲抑蛔鲞^(guò)兩家培訓(xùn)機(jī)構(gòu),一個(gè)是海同科技,另外一個(gè)就是達(dá)內(nèi)科技,就這兩家培訓(xùn)機(jī)構(gòu)我簡(jiǎn)單的說(shuō)一下我自己的看法吧,僅供同學(xué)們參考。

首先我說(shuō)下海同科技,這家培訓(xùn)機(jī)構(gòu),怎么說(shuō)呢,記得當(dāng)初我學(xué)習(xí)嵌入式的時(shí)候,從51--avr--arm--fpga 用了2年,實(shí)打?qū)嵉?年,沒(méi)日沒(méi)夜的學(xué)習(xí),才有點(diǎn)收獲。所以我是很清楚嵌入式學(xué)習(xí)的范圍之廣大。在這邊我也深刻的體會(huì)到了什么叫做效率,舉個(gè)例子 海同培訓(xùn)bootloader只有4節(jié)課,而且只講解vivi的啟動(dòng)代碼,而我當(dāng)初呢,bootloader中vivi/redboot/uboot花了3星期研究 不是說(shuō)我有多牛叉,我意思是 4節(jié)課能學(xué)到什么,作為老師,我有時(shí)候都覺(jué)得自己很牛叉,當(dāng)時(shí)自己鉆研了這么久的東西,如今教給學(xué)生居然可以在這么短的時(shí)間內(nèi)脫產(chǎn),不知道是我的教學(xué)水平高還是同學(xué)的接受能力好。說(shuō)下師資力量吧,我是一畢業(yè)就直接去軟件公司做IT開(kāi)發(fā)的,這方面經(jīng)驗(yàn)相當(dāng)豐富,做了有6個(gè)年頭了,我就想打算改行從事教師這個(gè)行業(yè),最終是海同成就了我這個(gè)夢(mèng)想,在此我也非常感謝海同科技。其他有幾個(gè)老師我就不敢恭維了,工作1年的linux+arm的工程師就被他們招收過(guò)去做講師,我也曾經(jīng)作為面試官面試過(guò),雖然他們也很優(yōu)秀,但是經(jīng)驗(yàn)難免會(huì)有些不足。曾經(jīng)的承諾年薪10萬(wàn),抑或是包就業(yè)到名企,都僅是些承諾罷了,師傅領(lǐng)進(jìn)門(mén),修行在個(gè)人,大家不要主觀認(rèn)為只要來(lái)了就肯定離名企不遠(yuǎn)了,其實(shí)這種觀點(diǎn)是完全錯(cuò)誤的。

再說(shuō)下達(dá)內(nèi)科技吧,我是覺(jué)得這家是很不錯(cuò)的,我絕對(duì)沒(méi)有在這里做廣告的意思,只是憑良心在說(shuō)話(huà)。我在這邊也待了大概快2年了,總的來(lái)說(shuō)我是很滿(mǎn)意的,在這里有一群很優(yōu)秀的同事(絕非說(shuō)海同不優(yōu)秀),30多個(gè)同事都是來(lái)自美國(guó)、加拿大的海外留學(xué)人員,都至少有5年以上從業(yè)經(jīng)驗(yàn)和項(xiàng)目開(kāi)發(fā)經(jīng)驗(yàn),大師說(shuō)不上,但是專(zhuān)家肯定不足為過(guò)。而且這邊的每一位學(xué)員的學(xué)習(xí)經(jīng)歷由一系列專(zhuān)家指導(dǎo)的:5—8技術(shù)專(zhuān)家擔(dān)任核心授課老師;1位項(xiàng)目經(jīng)理全程輔導(dǎo);1位班主任全程管理;1位職業(yè)素質(zhì)培訓(xùn)師指導(dǎo);1位職業(yè)發(fā)展顧問(wèn)指導(dǎo)、推薦就業(yè);10多位名企一線(xiàn)專(zhuān)家面授指點(diǎn)技術(shù)和求職。。。。在這邊就是覺(jué)得體系特別好,很遺憾后面因?yàn)閯e的原因我沒(méi)有繼續(xù)在這邊做下去,回想一下在達(dá)內(nèi)的那兩年,很是欣慰。。。所以我也是很推薦去達(dá)內(nèi)的,雖然同樣都是承諾進(jìn)名企,但是在這邊學(xué)習(xí)之后,如果你真的很用心,你真的離名企只有一步之遙。

三.認(rèn)真學(xué)習(xí)。既然選擇報(bào)了這個(gè)培訓(xùn)班,相信大家的初衷都是很好的,都是想學(xué)有所用,學(xué)有所為。所以認(rèn)真是必須的,要有堅(jiān)持不懈的毅力,一定不能輕言放棄,我見(jiàn)過(guò)很多學(xué)員剛開(kāi)始學(xué)的時(shí)候都是躊躇滿(mǎn)志的,學(xué)習(xí)難免比較枯燥,后面可能是堅(jiān)持不下來(lái)了吧,上過(guò)幾個(gè)星期的課之后就再也沒(méi)見(jiàn)過(guò)他的身影,除了惋惜還是惋惜。。。既然大家都交了錢(qián),為了這個(gè)錢(qián),為了交錢(qián)的父母,希望大家都能夠堅(jiān)持下來(lái),不經(jīng)歷風(fēng)雨怎能見(jiàn)彩虹,何況大家是在一個(gè)很好的環(huán)境當(dāng)中,吸取知識(shí)。。。希望大家能夠珍惜這樣一個(gè)機(jī)會(huì)。

以上就是我的一些建議和想法,可能有些只是我的一面之詞,但是我只是以我曾經(jīng)看到的經(jīng)歷過(guò)的事實(shí)說(shuō)話(huà)。希望想報(bào)培訓(xùn)班的同學(xué),要擦亮眼睛,選對(duì)培訓(xùn)機(jī)構(gòu);已經(jīng)報(bào)了培訓(xùn)班的同學(xué),都能夠打起12分的精神,好好學(xué)習(xí),以后進(jìn)一家自己心儀的企業(yè),成為企業(yè)中的中流砥柱。]]>

意味著你DM的bootloader程序已經(jīng)被破壞或者刪除!

首先,你要弄懂什么是JTAG?

1:JTAG(Joint Test Action Group;聯(lián)合測(cè)試行動(dòng)小組)是一種國(guó)際標(biāo)準(zhǔn)測(cè)試協(xié)議(IEEE 1149.1兼容),主要用于芯片內(nèi)部測(cè)試。現(xiàn)在多數(shù)的高級(jí)器件都支持JTAG協(xié)議,如DSP、FPGA器件等。標(biāo)準(zhǔn)的JTAG接口是4線(xiàn):TMS、TCK、TDI、TDO,分別為模式選擇、時(shí)鐘、數(shù)據(jù)輸入和數(shù)據(jù)輸出線(xiàn)。衛(wèi)視發(fā)燒聯(lián)盟論壇$ g- `4 z; v- q `

TAG最初是用來(lái)對(duì)芯片進(jìn)行測(cè)試的,JTAG的基本原理是在器件內(nèi)部定義一個(gè)TAP(Test Access Port;測(cè)試訪問(wèn)口)通過(guò)專(zhuān)用的JTAG測(cè)試工具對(duì)進(jìn)行內(nèi)部節(jié)點(diǎn)進(jìn)行測(cè)試。JTAG測(cè)試允許多個(gè)器件通過(guò)JTAG接口串聯(lián)在一起,形成一個(gè)JTAG鏈,能實(shí)現(xiàn)對(duì)各個(gè)器件分別測(cè)試。現(xiàn)在,JTAG接口還常用于實(shí)現(xiàn)ISP(In-System Programmable&#0;在線(xiàn)編程),對(duì)FLASH等器件進(jìn)行編程。

JTAG編程方式是在線(xiàn)編程,傳統(tǒng)生產(chǎn)流程中先對(duì)芯片進(jìn)行預(yù)編程現(xiàn)再裝到板上因此而改變,簡(jiǎn)化的流程為先固定器件到電路板上,再用JTAG編程,從而大大加快工程進(jìn)度。JTAG接口可對(duì)PSD芯片內(nèi)部的所有部件進(jìn)行編程8 Z: P6 `6 `- l- T, K" b8 t$ F

具有JTAG口的芯片都有如下JTAG引腳定義:

TCK——測(cè)試時(shí)鐘輸入;衛(wèi)視發(fā)燒聯(lián)盟論壇2 o# t3 z0 f$ I8 x% Z9 ^! ]; b

TDI——測(cè)試數(shù)據(jù)輸入,數(shù)據(jù)通過(guò)TDI輸入JTAG口;衛(wèi)視發(fā)燒聯(lián)盟論壇' H; e4 R$ Y' B) w x( B3 W% C

TDO——測(cè)試數(shù)據(jù)輸出,數(shù)據(jù)通過(guò)TDO從JTAG口輸出;

TMS——測(cè)試模式選擇,TMS用來(lái)設(shè)置JTAG口處于某種特定的測(cè)試模式。

可選引腳TRST——測(cè)試復(fù)位,輸入引腳,低電平有效。

含有JTAG口的芯片種類(lèi)較多,如CPU、DSP、CPLD等。衛(wèi)視發(fā)燒聯(lián)盟論壇) S$ l* H6 ~! ~+ W) r$ C; C

TAG內(nèi)部有一個(gè)狀態(tài)機(jī),稱(chēng)為T(mén)AP控制器。TAP控制器的狀態(tài)機(jī)通過(guò)TCK和TMS進(jìn)行狀態(tài)的改變,實(shí)現(xiàn)數(shù)據(jù)和指令的輸入。圖1為T(mén)AP控制器的狀態(tài)機(jī)框圖。; k$ {/ l) l& \' w9 w

2: JTAG芯片的邊界掃描寄存器: Y8 `& e- p0 G* d7 m

TAG標(biāo)準(zhǔn)定義了一個(gè)串行的移位寄存器。寄存器的每一個(gè)單元分配給IC芯片的相應(yīng)引腳,每一個(gè)獨(dú)立的單元稱(chēng)為BSC(Boundary-Scan Cell)邊界掃描單元。這個(gè)串聯(lián)的BSC在IC內(nèi)部構(gòu)成JTAG回路,所有的BSR(Boundary-Scan Register)邊界掃描寄存器通過(guò)JTAG測(cè)試激活,平時(shí)這些引腳保持正常的IC功能。圖2為具有JTAG口的IC內(nèi)部BSR單元與引腳的關(guān)系。" Q/ f& }7 u; t

3 : JTAG在線(xiàn)寫(xiě)Flash的硬件電路設(shè)計(jì)和與PC的連接方式! E7 x5 d" c W6 }& O

以含JTAG接口的StrongARM SA1110為例,F(xiàn)lash為Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分別接PC并口的2、3、4、11線(xiàn)上,通過(guò)程序?qū)?duì)JTAG口的控制指令和目標(biāo)代碼從PC的并口寫(xiě)入JTAG的BSR中。在設(shè)計(jì)PCB時(shí),必須將SA1110的數(shù)據(jù)線(xiàn)和地址線(xiàn)及控制線(xiàn)與Flash的地線(xiàn)線(xiàn)、數(shù)據(jù)線(xiàn)和控制線(xiàn)相連。因SA1110的數(shù)據(jù)線(xiàn)、地址線(xiàn)及控制線(xiàn)的引腳上都有其相應(yīng)BSC,只要用JTAG指令將數(shù)據(jù)、地址及控制信號(hào)送到其BSC中,就可通過(guò)BSC對(duì)應(yīng)的引腳將信號(hào)送給Flash,實(shí)現(xiàn)對(duì)Flash的操作。JTAG的系統(tǒng)板設(shè)計(jì)和連線(xiàn)關(guān)系如圖3所示。2 B9 T" ~' @' v; m

4: 通過(guò)使用TAP狀態(tài)機(jī)的指令實(shí)行對(duì)Flash的操作, k. D. j1 V! j

通過(guò)TCK、TMS的設(shè)置,可將JTAG設(shè)置為接收指令或數(shù)據(jù)狀態(tài)。JTAG常用指令如下:- z5 P; [$ \! _% j9 W

用此指令采樣BSC內(nèi)容或?qū)?shù)據(jù)寫(xiě)入BSC單元;

EXTEST——當(dāng)執(zhí)行此指令時(shí),BSC的內(nèi)容通過(guò)引腳送到其連接的相應(yīng)芯片的引腳,我們就是通過(guò)這種指令實(shí)現(xiàn)在線(xiàn)寫(xiě)Flash的;

BYPASS——此指令將一個(gè)一位寄存器軒于BSC的移位回路中,即僅有一個(gè)一位寄存器處于TDI和TDO之間。- y: \3 Y9 K; n8 K

在PCB電路設(shè)計(jì)好后,即可用程序先將對(duì)JTAG的控制指令,通過(guò)TDI送入JTAG控制器的指令寄存器中。再通過(guò)TDI將要寫(xiě)Flash的地址、數(shù)據(jù)及控制線(xiàn)信號(hào)入BSR中,并將數(shù)據(jù)鎖存到BSC中,用EXTEST指令通過(guò)BSC將寫(xiě)入Flash。-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->! U7 c. t9 x- ?2 C! [6 T$ }

5: 軟件編程

在線(xiàn)寫(xiě)Flash的程序用Turbo C編寫(xiě)。程序使用PC的并行口,將程序通過(guò)含有JTAG的芯片寫(xiě)入Flash芯片。程序先對(duì)PC的并口初始化,對(duì)JTAG口復(fù)位和測(cè)試,并讀Flash,判斷是否加鎖。如加鎖,必須先解鎖,方可進(jìn)行操作。寫(xiě)Flash之前,必須對(duì)其先擦除。將JTAG芯片設(shè)置在EXTEST模式,通過(guò)PC的并口,將目標(biāo)文件通過(guò)JTAG寫(xiě)入Flash,并在燒寫(xiě)完成后進(jìn)行校驗(yàn)。程序主流程如圖4所示。

通過(guò)JTAG的讀芯片ID子程序如下:-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->+ ?6 y. Z; G. R$ \, U2 W4 R

void id_command(void)+ T& B7 P4 L3 R/ x/ h+ ^- O- Q2 }

putp(1,0,IP); //Run-Test/Idle;使JTAG復(fù)位-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->5 L' S: h- X' C7 J. l2 W

putp(1,0,IP); //Run-Test/Idle

putp(1,0,IP); //Run-Test/Idlewww.lztvro.com$ D% o/ z5 c, A% W; h. B0 u

putp(1,0,IP); //Run-Test/Idle

putp(1,1,IP);-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->' a$ B# b: _- ?( j

putp(1,1,IP); //選擇指令寄存器www.lztvro.com% \. l4 l$ r* r, ?# l5 D3 _! @

putp(1,0,IP); //捕獲指令寄存器-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->6 n% q ?/ `$ d( h: i

putp(1,0,IP); /移位指令寄存器

putp(0,0,IP); //SA1110JTAG口指令長(zhǎng)度5位,IDCODE為01100

putp(1,0,IP);

putp(1,0,IP);:-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->; f5 b+ o i8 {

putp(0,0,IP);! J; y+ w' [8 F. a+ r( r( s$ I

putp(0,0,IP);% P; ]& |9 g8 j/ \

putp(0,1,IP); //退出指令寄存器* J) q$ [; B+ Q; J8 m* m

putp(1,1,IP); //更新指令寄存器,執(zhí)行指令寄存器中的指令

putp(1,0,IP); //Run-Test/Idle-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->, C# H* h8 V7 l( p- y. ?& M

putp(1,0,IP); //Run-Test/Idlewww.lztvro.com6 Y( O/ q! t5 ]( U

putp(1,0,IP); //Run-Test/Idle

putp(1,1,IP);www.lztvro.com' _3 F1 F4 E2 m' q

putp(1,0,IP);

if(check_id(SA1110ID))

error_out("failed to read device ID for the SA-1110");衛(wèi)視發(fā)燒聯(lián)盟論壇, S; k& p$ N& o0 [$ D7 l* x- ^

putp(1,1,IP); //退出數(shù)據(jù)寄存器' h! c" B/ e. p& z

putp(1,1,IP); //更新數(shù)據(jù)寄存器

putp(1,0,IP); //Run-Test/Idle,使JTAG復(fù)位

putp(1,0,IP); //Run-Test/Idle

putp(1,0,IP); //Run-Test/Idle衛(wèi)視發(fā)燒聯(lián)盟論壇+ k- G% x, N; ?9 S0 b; j6 {! l9 j: |

6 : 電路設(shè)計(jì)和編程中的注意事項(xiàng)

①Flash芯片的WE、CE、OE等控制線(xiàn)必須與SA1110的BSR相連。只有這樣,才能通過(guò)BSR控制Flash的相應(yīng)引腳。-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 -->8 ]! m( \5 N, h- e [' ^

②JTAG口與PC并口的連接線(xiàn)要盡量短,原則上不大于15cm。

③Flash在擦寫(xiě)和編程時(shí)所需的工作電流較大,在選用系統(tǒng)的供電芯片時(shí),必須加以考慮。www.lztvro.com# c4 v: S F* W' g6 v# `2 {1 W

④為提高對(duì)Flash的編程速度,盡量使TCK不低于6MHz,可編寫(xiě)燒寫(xiě)Flash程序時(shí)實(shí)現(xiàn)。

6 l: r2 w1 J: ?

6 l: r2 w1 J: ?什么是BootLoader,它的作用是什么?) |' B# C7 F2 k6 [2 F' H

Bootloader是在操作系統(tǒng)運(yùn)行之前執(zhí)行的一段小程序。通過(guò)這段小程序,我們可以初始化硬件設(shè)備、建立內(nèi)存空間的映射表,從而建立適當(dāng)?shù)南到y(tǒng)軟硬件環(huán)境,為最終調(diào)用操作系統(tǒng)內(nèi)核做好準(zhǔn)備。+ N" u# c) }9 Q( r/ U3 `

對(duì)于嵌入式系統(tǒng),Bootloader是基于特定硬件平臺(tái)來(lái)實(shí)現(xiàn)的。因此,幾乎不可能為所有的嵌入式系統(tǒng)建立一個(gè)通用的Bootloader,不同的處理器架構(gòu)都有不同的Bootloader。

Bootloader不但依賴(lài)于CPU的體系結(jié)構(gòu),而且依賴(lài)于嵌入式系統(tǒng)板級(jí)設(shè)備的配置。對(duì)于2塊不同的嵌入式板而言,即使它們使用同一種處理器,要想讓運(yùn)行在一塊板子上的Bootloader程序也能運(yùn)行在另一塊板子上,一般也都需要修改Bootloader的源程序。

快快去嘗試修復(fù)你DM的Bootloader程序,來(lái)拯救你的DM500!

-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 --> {. m% \; W+ E$ |

-- DM500S,DM800HD,DM共享,中衛(wèi),斯維克天線(xiàn),成都衛(wèi)星電視安裝,hibox,openbox,百昌525,百昌222,ak47,icool 2g,138,adbox,中九,數(shù)碼低端機(jī),藝華,華人,八切一,四切一,功分器 --> {. m% \; W+ E$ |]]>

首先,對(duì)于RS232通訊要了解,即在232通訊當(dāng)中,“-3V~-15V”表示邏輯1,“+3V~+15V”表示邏輯0。現(xiàn)在我們來(lái)對(duì)電路進(jìn)行分析一下。

下面先看單片機(jī)這邊:當(dāng)單片機(jī)TXD2端口放送數(shù)據(jù)時(shí),當(dāng)為低電平“0”時(shí),光耦導(dǎo)通,+6V經(jīng)過(guò)RX、R52、D13、R51、光耦1,2腳到地形成回路。此回路阻值大致為2.2K+2.2K+1.6K=6K,I=6/6K=1mA。在這種情況下,RX大概在5.幾V,故PC機(jī)接收為邏輯“0”。與單片機(jī)這邊發(fā)送相一致。由于此時(shí)1mA為截止,驅(qū)動(dòng)不了發(fā)光二極管,但能導(dǎo)通。故對(duì)TX沒(méi)有影響。

同理當(dāng)TXD2為高電平“1”時(shí),IC14截止,RX為低電平,+6經(jīng)過(guò)C21、C20、R52回到RX,注意G3的位置,此時(shí)RX由于放電處于負(fù)壓狀態(tài),故為邏輯“1”,與發(fā)送狀態(tài)相一致。

接下倆看看PC機(jī)這邊。當(dāng)TX發(fā)送“0”,極為高電平時(shí),IC13導(dǎo)通,RXD2為低電平,故為“0”。當(dāng)TX為“1”,即為“-3~-15V”時(shí),明顯IC13截止而RXD2為高電平。

總體上說(shuō),RS232就是一個(gè)電平轉(zhuǎn)換的過(guò)程,不管是上面所搭的電路還是MAX232都是電平轉(zhuǎn)換。但在調(diào)試的過(guò)程當(dāng)中,發(fā)現(xiàn)PC機(jī)發(fā)送數(shù)據(jù)時(shí),單片機(jī)接受的是發(fā)送數(shù)據(jù)的2倍。只有講接收到的數(shù)除以2才能得到實(shí)際發(fā)送的數(shù)據(jù)。

這一問(wèn)題有待解決。]]>

tory burch shoes Quasi-dynamic high-fidelity real-time image capture and compres

MAC Cosmetics Cheap PE3293 high-performance PLL and its application _ of Chemist

p90x discount Heat Energy Meter Based on PIC Microcontroller Development of Chem]]>

<P>1、有一定的上網(wǎng)時(shí)間,并且有喜歡在網(wǎng)上表現(xiàn)。<br>2、每個(gè)人都可以申請(qǐng)成為成為現(xiàn)有版塊的版主,及根據(jù)自已的喜好申請(qǐng)新開(kāi)版塊成為版主。<br>3、不得申請(qǐng)與中華人民共和國(guó)法律相抵觸的內(nèi)容版塊.<br>4、所有的想做版主的都在這里跟貼說(shuō)明。<br>5、所有申請(qǐng)版主的人請(qǐng)先在自己想做版主的欄目多發(fā)一些有價(jià)值的貼,再申請(qǐng)會(huì)好些。(如果現(xiàn)有欄目沒(méi)有適合你的,而且也是電子及電腦行業(yè)的,可以先申請(qǐng)版主。)<br>6、非常歡迎有自己的產(chǎn)品的及能系統(tǒng)介紹自己所喜歡行業(yè)知識(shí)的人員加入。<br>7、版主可以在自己所管欄目發(fā)表自己產(chǎn)品(必需與欄目相關(guān))<br>8、必須熟悉網(wǎng)站建設(shè)和自己版面的內(nèi)容。<br>9、必須每天更新所負(fù)責(zé)版面的內(nèi)容(最少一篇文章或軟件)和解答他人提出的問(wèn)題。<br>10、登記真實(shí)姓名、地址、本論壇id等</P>

<P><br>版主權(quán)限和利益分享:<br>1、可擁有本論壇的全部權(quán)限;<br>2、可享受本站產(chǎn)品的成本價(jià)或代理價(jià)格(成為版主2個(gè)月后;<br>3、享受項(xiàng)目合作機(jī)會(huì);<br>4、優(yōu)先推薦高薪工作機(jī)會(huì);<br>有意者請(qǐng)與站長(zhǎng)聯(lián)系:email:<a target="_blank" >21control@21cn.com</A></P>

<P><br>請(qǐng)對(duì)此提議有信心和興趣的朋友跟貼。<br></P><br><br><br><br>

<P>附版主申請(qǐng)表格:</P>

<P><br>==================================================================<br>您在本論壇ID: <br>性 別:<br>要申請(qǐng)的版面: <br>目前居住城市:<br>職業(yè)以及特長(zhǎng): <br>您的聯(lián)系方式:(QQ/ICQ/MSN等)<br>日均上網(wǎng)時(shí)間:<br>是否做過(guò)版主:(主要指其他的論壇)<br>熟識(shí)的版面:(本論壇上的)<br>==================================================================<br>您認(rèn)為版主的職責(zé)是什么?</P>

<P>==================================================================<br>您申請(qǐng)?jiān)摪姘嬷鞯脑敿?xì)理由是什么?<br>(主要闡明您為什么要做該版版主,以及讓我們相信,您有管好該版的能力)</P>

<P>==================================================================<br>對(duì)您所申請(qǐng)的版面,您認(rèn)為應(yīng)該如何發(fā)展?</P>

]]>

LED 驅(qū)動(dòng)芯片的動(dòng)態(tài)響應(yīng)特性經(jīng)常被忽略,但卻是相當(dāng)重要的一個(gè)特性。動(dòng)態(tài)響應(yīng)影響LED顯示屏的影像質(zhì)量,如灰階、線(xiàn)性度、EMI、信賴(lài)性。雖然這些特性彼此間有取舍關(guān)系.但是好的驅(qū)動(dòng)芯片應(yīng)該能夠在這些特性中取得較佳的平衡。本文將探討動(dòng)態(tài)響應(yīng)的重要性及LED驅(qū)動(dòng)芯片與電路板設(shè)計(jì)技術(shù),以協(xié)助工程師設(shè)計(jì)出影像質(zhì)量良好的顯示屏。標(biāo) 簽 驅(qū)動(dòng)器 交流響應(yīng):突破 driver AC respanse overshoot

AC responses of LED drivers are critical but usually ignored in LED display applications.AC responses affect the major performance of LED display panels,such as grayscales, linearity, EMI, and reliability. Although there is trade-off w ithin these requirements, LED drivers can provide balance.This article will further explain the importance of the AC responses of LED drivers and PCB design techniques to help engineers to design LED panels with good grayscale images]]>

小巧玲瓏的龍芯II福瓏迷你電腦,而這臺(tái)電腦滿(mǎn)負(fù)載功率也不超過(guò)20W

龍芯II福瓏迷你電腦前斜視圖。體積大概和一個(gè)外置硬盤(pán)盒差不多。

龍芯II福瓏迷你電腦后斜視圖。

前面板上放置了4個(gè)USB2.0、麥克風(fēng)、耳機(jī)、線(xiàn)性輸出插口;紅外IO窗口,以及一組指示燈和復(fù)位、電源開(kāi)關(guān)。

后面板上放置了鍵鼠共用的PS2口、網(wǎng)卡RJ45、顯示器模擬輸出、視頻S端、串口插座以及直流12V電源插座

龍芯II福瓏迷你電腦底面

底面的銘牌,我們拿到的這臺(tái)樣品配置并不高。256M內(nèi)存/40G硬盤(pán)/666MHz的龍芯2E處理器

拆除外殼后的前斜視圖

拆除外殼后的底前斜視圖

NEC的USB2.0控制芯片

ATI Radeon 7000M顯示芯片,旁邊的小方塊是16M DDR顯示內(nèi)存芯片。

龍芯2E處理器,意法半導(dǎo)體代加工。采用90nm工藝。 這款處理器十分節(jié)能,峰值功率僅有4W,這個(gè)優(yōu)勢(shì)讓龍芯2E芯片可用領(lǐng)域大幅拓展。 龍芯2E上方的芯片為Altera Cyclone II FPGA,這是一顆現(xiàn)場(chǎng)可編程門(mén)陣列芯片, 通過(guò)編程控制,這顆芯片起到了一個(gè)簡(jiǎn)單的北橋芯片的作用。

]]>

Atom E600C系列研發(fā)代號(hào)為Stellarton,今年9月份的IDF大會(huì)上首次公開(kāi),今天則正式發(fā)布。該系列實(shí)際上就是將一顆代號(hào)Tunnel Creek的Atom E600嵌入式處理器核心與Altera FPGA封裝在一顆芯片上。基于FPGA的可編程特性,客戶(hù)廠商可對(duì)這顆二合一處理器進(jìn)行不同的配置,以滿(mǎn)足不同應(yīng)用的需要。

對(duì)于下游廠商來(lái)說(shuō),使用這顆二合一處理器可以簡(jiǎn)便的開(kāi)發(fā)出針對(duì)不同市場(chǎng)需求的應(yīng)用處理器產(chǎn)品,比如工控機(jī)、便攜式醫(yī)療設(shè)備、通訊設(shè)備、視覺(jué)系統(tǒng)、VOIP設(shè)備、高性能可編程邏輯控制器、嵌入式計(jì)算機(jī)等。同時(shí),由于省去了為其搭配FPGA等芯片的步驟,可以節(jié)約電路板空間,控制庫(kù)存和成本,簡(jiǎn)化制造過(guò)程,并且只需要依賴(lài)一家廠商提供服務(wù)。

核心架構(gòu)

Intel為面向嵌入式產(chǎn)品提供7年生命周期的制造支持,Atom E600C系列現(xiàn)有6款型號(hào),E665CT、E645CT、E665C和E645C將在60天內(nèi)上市,E625CT和E625C則會(huì)在明年一季度出貨。全系列產(chǎn)品的千顆單價(jià)在61到106美元之間。目前,嵌入式系統(tǒng)開(kāi)發(fā)商Kontron已經(jīng)可以提供基于Atom E600C的工程樣板,明年二季度開(kāi)始量產(chǎn)。

型號(hào)列表

開(kāi)發(fā)平臺(tái)

新一代 FPGA的速度變得越來(lái)越快,密度變得越來(lái)越高,邏輯資源也越來(lái)越多。那么如何才能確保功耗不隨這些一起增加呢?很多設(shè)計(jì)抉擇可以影響系統(tǒng)的功耗,這些抉擇包括從顯見(jiàn)的器件選擇到細(xì)小的基于使用頻率的狀態(tài)機(jī)值的選擇等。

為了更好地理解本文將要討論的設(shè)計(jì)技巧為什么能夠節(jié)省功耗,我們先對(duì)功耗做一個(gè)簡(jiǎn)單介紹。

功耗包含兩個(gè)因素:動(dòng)態(tài)功耗和靜態(tài)功耗。動(dòng)態(tài)功耗是指對(duì)器件內(nèi)的容性負(fù)載充放電所需的功耗。它很大程度上取決于頻率、電壓和負(fù)載。這三個(gè)變量中的每個(gè)變量均在您的某種控制之下。

動(dòng)態(tài)功耗 = 電容×電壓2×頻率

靜態(tài)功耗是指由器件中所有晶體管的泄漏電流(源極到漏極以及柵極泄漏,常常集中為靜止電流)引起的功耗,以及任何其他恒定功耗需求之和。泄漏電流很大程度上取決于結(jié)溫和晶體管尺寸。

恒定功耗需求包括因終接(如上拉電阻)而造成的電流泄漏。沒(méi)有多少措施可以采用來(lái)影響泄漏,但恒定功耗可以得到控制。

盡早考慮功耗

您在設(shè)計(jì)的早期階段做出的功耗決定影響最大。決定采用什么元件對(duì)功耗具有重大意義,而在時(shí)鐘上插入一個(gè) BUFGMUX 則影響甚微。對(duì)功耗的考慮越早越好。

恰當(dāng)?shù)脑?

并不是所有元件都具有相同的靜止功耗。根據(jù)普遍規(guī)則,器件工藝技術(shù)尺寸越小,泄漏功耗越大。但并不是所有工藝技術(shù)都一樣。例如,對(duì)于 90 nm 技術(shù)來(lái)說(shuō),Virtex-4 器件與其他 90 nm FPGA 技術(shù)之間在靜止功耗方面存在顯著差異,

然而,在靜止功耗隨工藝技術(shù)縮小而增加的同時(shí),動(dòng)態(tài)功耗卻隨之減小,這是由于較小的工藝有著更低的電壓和電容。考慮好哪種功耗對(duì)你的設(shè)計(jì)影響更大——待機(jī)(靜止)功耗還是動(dòng)態(tài)功耗。

除通用切片邏輯單元外,所有Xilinx器件都具有專(zhuān)門(mén)邏輯。其形式有塊 RAM、18×18 乘法器、DSP48 塊、SRL16s,以及其他邏輯。這不僅在于專(zhuān)門(mén)邏輯具有更高的性能,還在于它們具有更低的密度,因而對(duì)于相同的操作可以消耗較少的功率。評(píng)估您的器件選項(xiàng)時(shí),請(qǐng)考慮專(zhuān)門(mén)邏輯的類(lèi)型和數(shù)量。

選擇適當(dāng)?shù)?I/O 標(biāo)準(zhǔn)也可以節(jié)省功耗。這些都是簡(jiǎn)單的決定,如選擇最低的驅(qū)動(dòng)強(qiáng)度或較低的電壓標(biāo)準(zhǔn)。當(dāng)系統(tǒng)速度要求使用高功率 I/O 標(biāo)準(zhǔn)時(shí),計(jì)劃一個(gè)缺省狀態(tài)以降低功耗。有的 I/O 標(biāo)準(zhǔn)(如 GTL/+)需要使用一個(gè)上拉電阻才能正常工作。因此如果該 I/O 的缺省狀態(tài)為高電平而不是低電平,就可以節(jié)省通過(guò)該終接電阻的直流功耗。對(duì)于 GTL+,將50Ω終接電阻的適當(dāng)缺省狀態(tài)設(shè)置為 1.5V,可使每個(gè) I/O 節(jié)省功耗 30 mA。

數(shù)據(jù)使能

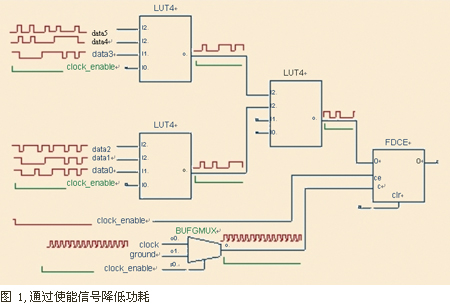

當(dāng)總線(xiàn)上的數(shù)據(jù)與寄存器相關(guān)時(shí),經(jīng)常使用片選或時(shí)鐘使能邏輯來(lái)控制寄存器的使能。進(jìn)一步來(lái)說(shuō),盡早對(duì)該邏輯進(jìn)行“數(shù)據(jù)使能”,以阻止數(shù)據(jù)總線(xiàn)與時(shí)鐘使能寄存器組合邏輯之間不必要的轉(zhuǎn)換,如圖 1 所示。紅色波形表示原設(shè)計(jì);綠色波形表示修改后的設(shè)計(jì)。

另一種選擇是在電路板上而不是在芯片上進(jìn)行這種“數(shù)據(jù)使能”。以盡可能減小處理器時(shí)鐘周期。此概念是使用 CPLD 從處理器卸載簡(jiǎn)單任務(wù),以便使其更長(zhǎng)時(shí)間地處于待機(jī)模式。

讓我們來(lái)看一個(gè)在狀態(tài) 7 和狀態(tài) 8 之間頻繁進(jìn)行狀態(tài)轉(zhuǎn)換的狀態(tài)機(jī)。如果您為該狀態(tài)機(jī)選擇二進(jìn)制編碼,將意味著對(duì)于每次狀態(tài) 7 和狀態(tài) 8 之間的狀態(tài)轉(zhuǎn)換,將有四位需要改變狀態(tài),如表 1 所示。如果狀態(tài)機(jī)采用格雷碼而不是二進(jìn)制碼來(lái)設(shè)計(jì),則這兩個(gè)狀態(tài)之間的轉(zhuǎn)移所需的邏輯轉(zhuǎn)換的數(shù)量將降至僅一位。另外,如果將狀態(tài) 7 和 8 分別編碼為 0010 和 0011,也可以達(dá)到同樣的效果。

時(shí)鐘管理

在一個(gè)設(shè)計(jì)的所有吸收功耗的信號(hào)當(dāng)中,時(shí)鐘是罪魁禍?zhǔn)住km然一個(gè)時(shí)鐘可能運(yùn)行在 100 MHz,但從該時(shí)鐘派生出的信號(hào)卻通常運(yùn)行在主時(shí)鐘頻率的較小分量(通常為 12% ~ 15%)。此外,時(shí)鐘的扇出一般也比較高——這兩個(gè)因素顯示,為了降低功耗,應(yīng)當(dāng)認(rèn)真研究時(shí)鐘。

如果設(shè)計(jì)的某個(gè)部分可以處于非活動(dòng)狀態(tài),則可以考慮使用一個(gè) BUFG-MUX 來(lái)禁止時(shí)鐘樹(shù)翻轉(zhuǎn),而不是使用時(shí)鐘使能。時(shí)鐘使能將阻止寄存器進(jìn)行不必要的翻轉(zhuǎn),但時(shí)鐘樹(shù)仍然會(huì)翻轉(zhuǎn),消耗功率。不過(guò)采用時(shí)鐘使能總比什么措施也沒(méi)有強(qiáng)。

隔離時(shí)鐘以使用最少數(shù)量的信號(hào)區(qū)。不使用的時(shí)鐘樹(shù)信號(hào)區(qū)不會(huì)翻轉(zhuǎn),從而降低該時(shí)鐘網(wǎng)絡(luò)的負(fù)載。仔細(xì)布局可以在不影響實(shí)際設(shè)計(jì)的情況下達(dá)到此目標(biāo)。

對(duì) FPGA 顯然也可以使用同一概念。雖然 FPGA 不一定擁有待機(jī)模式,但使用一個(gè) CPLD 中途欄截總線(xiàn)數(shù)據(jù)并有選擇地將數(shù)據(jù)饋送到 FPGA 也可以省去不必要的輸入轉(zhuǎn)換。

CoolRunner-II CPLD 包含一種稱(chēng)為“數(shù)據(jù)門(mén)控”的功能,可以禁止引腳上的邏輯轉(zhuǎn)換到達(dá) CPLD 的內(nèi)部邏輯。該數(shù)據(jù)門(mén)控使能可通過(guò)片上邏輯或引腳來(lái)控制。

狀態(tài)機(jī)設(shè)計(jì)

根據(jù)預(yù)測(cè)的下一狀態(tài)條件列舉狀態(tài)機(jī),并選擇常態(tài)之間轉(zhuǎn)換位較少的狀態(tài)值。這樣,您就能夠盡可能減少狀態(tài)機(jī)網(wǎng)絡(luò)的轉(zhuǎn)換量(頻率)。確定常態(tài)轉(zhuǎn)換和選擇適當(dāng)?shù)臓顟B(tài)值,是降低功耗且對(duì)設(shè)計(jì)影響較小的一種簡(jiǎn)單方法。編碼形式越簡(jiǎn)單(一位有效編碼或格雷碼),使用的解碼邏輯也會(huì)越少。

功耗估算工具

賽靈思提供了兩種形式的功耗估算工具:一種叫做 Web Power Tools 的設(shè)計(jì)前工具和一種叫做 Xpower 的設(shè)計(jì)后工具。Web Power Tools 可通過(guò) www.xilinx.com/cn/power 獲得,它提供了根據(jù)邏輯利用率大概估計(jì)做出的功耗估算。利用它,您可以?xún)H憑設(shè)計(jì)利用率估計(jì)就能獲得功耗評(píng)估,而無(wú)需實(shí)際設(shè)計(jì)文件。

XPower 是一種設(shè)計(jì)后工具,用于分析實(shí)際器件利用率,并結(jié)合實(shí)際的適配后 (post-fit) 仿真數(shù)據(jù)(VCD 文件格式),給出實(shí)際功耗數(shù)據(jù)。利用 Xpower,您可以在完全不接觸芯片的情況下分析設(shè)計(jì)改變對(duì)總功耗的影響。

基于 Web 的功耗工具

基于 Web 的功耗估計(jì)是在設(shè)計(jì)流程的早期獲得器件功耗情況的最快捷和最方便的方法。這些工具每個(gè)季度都會(huì)發(fā)布新版本,因此信息總是最新的,且不需要安裝或下載,只需要擁有互聯(lián)網(wǎng)連接和 Web 瀏覽器即可。您可以指定設(shè)計(jì)參數(shù)并保存和加載設(shè)計(jì)設(shè)置,免去了通過(guò)交互使用重新輸入設(shè)計(jì)參數(shù)的麻煩。只要有對(duì)設(shè)計(jì)行為的估計(jì)并選定目標(biāo)器件即可開(kāi)始。

Xpower:集成的設(shè)計(jì)專(zhuān)用功耗分析

Xpower 是所有 Xilinx ISE設(shè)計(jì)工具的一個(gè)免費(fèi)組件,您可以利用它對(duì)您的基于設(shè)計(jì)的功耗需求進(jìn)行詳細(xì)得多的估計(jì)。XPower 是在映射或布局和布線(xiàn)后設(shè)計(jì)的基礎(chǔ)上對(duì)器件功耗進(jìn)行估計(jì)的。

對(duì)于成熟的投產(chǎn)的 FPGA 和 CPLD,XPower 計(jì)算出的功耗估計(jì)的平均設(shè)計(jì)批量誤差 (suite error) 小于 10%。它將把器件數(shù)據(jù)與您的設(shè)計(jì)文件結(jié)合起來(lái)綜合考慮,并按照您的專(zhuān)門(mén)設(shè)計(jì)信息給出估計(jì)器件功耗的高精度報(bào)告。

XPower直接集成在 ISE 軟件中,可提供層次化的詳細(xì)的功耗顯示、詳細(xì)的總結(jié)報(bào)告和功耗向?qū)?即使是新用戶(hù)也可輕易上手。XPower 可接受仿真的設(shè)計(jì)活動(dòng)數(shù)據(jù),并可以 GUI 模式和批處理模式運(yùn)行。

XPower 將考慮設(shè)計(jì)中的每個(gè)網(wǎng)絡(luò)和邏輯元素。ISE 設(shè)計(jì)文件提供準(zhǔn)確的資源使用情況;XPower 交叉參考布線(xiàn)信息以及特性化電容數(shù)據(jù)。于是物理資源針對(duì)電容進(jìn)行特性化。設(shè)計(jì)特性化將對(duì)新器件持續(xù)進(jìn)行,以給出最精確的結(jié)果。Xpower 使用了網(wǎng)絡(luò)翻轉(zhuǎn)速率和輸出負(fù)載。然后 XPower 計(jì)算功耗和結(jié)溫,還可以顯示單個(gè)網(wǎng)絡(luò)的功耗數(shù)據(jù)。

結(jié)論

對(duì)更便宜和更簡(jiǎn)單的熱管理以及與前沿 FPGA 不斷提高的功耗需求相匹配的電源的不斷增長(zhǎng)的需求,將低功耗設(shè)計(jì)的概念提升到一個(gè)全新的高度。賽靈思最新器件 Virtex-4 FPGA 提供了 90 nm 工藝技術(shù)的高性能,卻避免了預(yù)想中靜態(tài)功耗的顯著增大。使用賽靈思功耗估算工具并遵循低功耗設(shè)計(jì)考慮事項(xiàng),滿(mǎn)足您的功耗目標(biāo)將比以往任何時(shí)候都更加容易。

]]>功能特點(diǎn):

1、支持Xilinx公司的FPGA設(shè)計(jì);

2、采用Spartan3的兼容設(shè)計(jì),芯片為:XC3S400PQ208;

3、板上電源:5V、1.2V、2.5V;

4、PQ208封裝,滿(mǎn)足多IO 設(shè)計(jì)需求;

5、支持Xilinx的JTGA在線(xiàn)配置調(diào)試;

6、支持XCF02S芯片配置和程序固化;

7、4位7段數(shù)碼管;

8、8個(gè)按鍵輸入;

9、8個(gè)發(fā)光二極管;

10、標(biāo)準(zhǔn)RS232串行接口;

11、PS2鼠標(biāo)、鍵盤(pán)接口;

12、音頻輸出接口;

13、蜂鳴器輸出接口;

14、VGA視頻接口;

15、支持I2C芯片AT24CXX系列芯片的讀寫(xiě);

16、支持1602液晶顯示

17、支持帶漢字庫(kù)的12864的液晶顯示(如OCMJ48);

18、256 K16bit SRAM, 可以作為動(dòng)態(tài)存儲(chǔ)芯片;

19、32位SDRAM(可達(dá)128M), 滿(mǎn)足大容量需求進(jìn)行SOPC程序存儲(chǔ);

20、50M晶振, 可以?xún)?nèi)部倍頻滿(mǎn)足高速設(shè)計(jì)需求;

21、晶振可插拔, 更改為其他頻率.

光盤(pán)內(nèi)容及說(shuō)明:

1) 、閱讀器 Acrobat Reader 6.0

2) 、數(shù)據(jù)手冊(cè) FPGA芯片數(shù)據(jù)手冊(cè),以及外圍芯片(如flashsdramsramlcd等)的數(shù)據(jù)手冊(cè)

3) 、安裝指南 ise安裝指南

4) 、軟件教程 簡(jiǎn)明中文教程

5) 、調(diào)試工具 測(cè)試工具,包含串口通信測(cè)試程序

6) 、原理圖 開(kāi)發(fā)板原理圖

7) 、器件選型 xilinx產(chǎn)品軟硬件選型指南

8) 、電源選型 xilinx產(chǎn)品電源選型指南

9) 、用戶(hù)手冊(cè) 用戶(hù)手冊(cè),請(qǐng)用Acrobat Reader瀏覽

10) 、examples 開(kāi)發(fā)板例子(包含工程設(shè)計(jì)和文檔說(shuō)明,含PS2 MouseKeyboardVGARS232LCDLEDSOPC等)

11) 、軟件部分(software) ise_6.3或ise_web.

光盤(pán)所帶的例子程序

sw_demo按鍵測(cè)試程序;seg_demo 7段數(shù)碼管時(shí)鐘顯示程序;imageshow從SRAM中讀取數(shù)據(jù)并顯示程序;

lcd_demo液晶模塊顯示程序(128x64帶漢字庫(kù));led_demo發(fā)光二極管顯示程序;

mouse_seg鼠標(biāo)移動(dòng)并顯示在7段數(shù)碼管上程序;uart_demo RS232串行通信程序,使用串口助手接收發(fā)送數(shù)據(jù);

vga_demo彩條信號(hào)顯示程序;music_demo音頻發(fā)生器,外接音箱即可用按鍵演奏程序;sram_demo讀寫(xiě)sram程序;

lcd_demo_1602液晶1602的讀寫(xiě)顯示程序;edk_led使用嵌入式內(nèi)核控制led程序;

edk_uart使用嵌入式內(nèi)核控制串口程序;edk_sdram使用嵌入式內(nèi)核測(cè)試sdram程序;^-^其他例子不斷更新中.

更多產(chǎn)品信息,歡迎登錄網(wǎng)站或電話(huà)查詢(xún)。

]]>

防拷貝技術(shù)也不錯(cuò)。

1.本質(zhì)結(jié)構(gòu)不一樣

ACTEL是基于flash結(jié)構(gòu),ALTETA、XINLINX(賽林思)和Lattice都是采用SRAM結(jié)構(gòu),掉電數(shù)據(jù)丟失,所以需要一塊配置芯片,而ACTEL無(wú)須配置。

2.安全性-無(wú)法破解

ACTEL FPGA內(nèi)部有2重保密功能:一個(gè)是128位Flashlock加密,一個(gè)是128位的AES的加密(全部在軟件里面自由設(shè)置),真正達(dá)到保護(hù)您的知識(shí)產(chǎn)權(quán)。Flashlock密鑰是保護(hù)芯片,防止他人進(jìn)行效驗(yàn)、編程、擦除。只有正確的128位Flashlock密鑰才能進(jìn)行對(duì)芯片擦除重寫(xiě)。2的64次方已經(jīng)很大了,2的128次方就更大了。就算運(yùn)氣好,把Flashlock密碼破解了,但程序代碼又是使用128位的AES加密。如果用世界上最快的計(jì)算機(jī)也要1百億年。所以ACTEL的代碼基本可以實(shí)現(xiàn)網(wǎng)上傳輸,就算人家截了也沒(méi)有用。也許有人會(huì)說(shuō)用反向工程,采取磨芯片獲取開(kāi)關(guān)狀態(tài)。但是ACTEL的晶體管都在7層金屬銅之下,如果把前7層金屬去掉了,還不破壞布線(xiàn)結(jié)構(gòu)和內(nèi)部晶體管,這基本是不可能的,這也是軍事和航空中全部使用ACTEL的原因。

3.上電即運(yùn)行

ACTEL與其他公司的FPGA相比的另一個(gè)優(yōu)點(diǎn)就是上電即運(yùn)行。這個(gè)特性有助于系統(tǒng)組件的初始化、處理器喚醒緊急任務(wù)的執(zhí)行,而ALTERA、XINLINX的FPGA上電到正常工作需要0.2秒的時(shí)間。這一點(diǎn)也正是ACTEL廣泛用于航空或者軍事領(lǐng)域的原因。例如:在不停車(chē)收費(fèi)系統(tǒng)中,就利用了ACTEL的上電就運(yùn)行。汽車(chē)在高速公路上行使的速度特別快,而在遠(yuǎn)離收費(fèi)系統(tǒng)中,FPGA是處于掉電狀態(tài).當(dāng)接近收費(fèi)區(qū)的時(shí)候,FPGA啟動(dòng)工作,所以設(shè)計(jì)中必須要滿(mǎn)足FPGA上電就工作,SRAM型的FPGA上電配置要200MS,有點(diǎn)不妥,可能導(dǎo)致結(jié)果是:等到FPGA開(kāi)始工作的時(shí)候,車(chē)已經(jīng)開(kāi)出了射頻區(qū),車(chē)載發(fā)送的數(shù)據(jù)主站無(wú)法收到。

4.真正的單芯片解決方案

ACTEL是flash架構(gòu)的FPGA,而ALTERA和XINLINX的都是SRAM架構(gòu),掉電數(shù)據(jù)丟失,所以一般需要外加一個(gè)配置芯片。由于ACTEL是flash架構(gòu)的FPGA,所以不要配置芯片,而且功耗更低。ACTEL的FUSION系列更是內(nèi)部帶模擬功能,內(nèi)部有電流監(jiān)控,電壓監(jiān)控,12位AD,RTC掉電喚醒等等.IGOOL系列更是為手持設(shè)備量身定做,靜態(tài)功耗為5微瓦,最小封裝僅為4mm*4mm,比業(yè)界最低功耗的CPLD節(jié)省500倍以上。

5.無(wú)可挑剔的穩(wěn)定性

ACTEL具有固件免疫能力,就是任何高能量的中子和a粒子撞擊器件都絲毫沒(méi)有影響,但是SRAM型的FPGA是不能承受高能量粒子的撞擊,不能適合惡劣的環(huán)境。目前上海中科院物理研究所承擔(dān)的"嫦娥1號(hào)"項(xiàng)目中,就是使用的ACTEL系列反熔絲系列的芯片。這個(gè)也是ACTEL在軍事、汽車(chē)行業(yè)中的優(yōu)勢(shì)所在。

6.完整免費(fèi)的開(kāi)發(fā)平臺(tái)

軟件完全免費(fèi),內(nèi)部集成了業(yè)界最好的綜合工具synplify,仿真最好的工具M(jìn)ODESIM等,不收取任何費(fèi)用,全部自動(dòng)完成安裝,軟件開(kāi)發(fā)簡(jiǎn)單,使用方便。我們有一系列詳細(xì)的例程(PLL,RAM,FIFO,Flashrom,動(dòng)態(tài)PLL),讓您輕松實(shí)現(xiàn)代碼的移植。同時(shí)最新的2本ACTEL書(shū)籍(ACTEL原理與應(yīng)用和ACTEL實(shí)驗(yàn)例程)和便宜的開(kāi)發(fā)板讓您一個(gè)星期就可以完全掌握ACTEL設(shè)計(jì)的精髓。

7.ACTEL內(nèi)部包含ARM7或CORTEX_M1處理器

帶M7和M1前綴的FPGA都支持ARM處理器,也就是FPGA內(nèi)部不單可以實(shí)現(xiàn)FPGA的功能,還有ARM處理器,實(shí)現(xiàn)“FPGA+ARM”的組合方案,就象ALTETA里面的NIOS II。

8.完全替代業(yè)界的CPLD器件

ACTEL FPGA擁有3-300萬(wàn)門(mén)之間的器件,在同等價(jià)格中,我們不但具備CPLD全部的功能,還具備PLL,RAM,F(xiàn)IFO,1K的flashROM,128位的AES密鑰,絕對(duì)的可靠性。這樣的話(huà),我們還有什么理由不選用ACTEL。

本人不是ACTEL的代理,以上摘自EDN.

防拷貝雖然不利于技術(shù)交流,對(duì)于企業(yè)可是生死存活的事情,相信還是有市場(chǎng)的。]]>

為了在競(jìng)爭(zhēng)中占據(jù)主動(dòng),PLD市場(chǎng)勢(shì)均力敵的兩大領(lǐng)導(dǎo)廠商Xilinx與Altera新近分別宣布他們的下一代FPGA產(chǎn)品都將采用高k金屬柵技術(shù)的28nm工藝,以滿(mǎn)足諸如云計(jì)算、移動(dòng)互聯(lián)網(wǎng)和3G應(yīng)用等領(lǐng)域所不斷增長(zhǎng)的帶寬需求。因?yàn)镻LD器件采用更高技術(shù)的工藝節(jié)點(diǎn)制造,無(wú)疑可以降低成本、提升性能,尤其是能夠改進(jìn)一直以來(lái)為ASIC所詬病的功耗水平,以適應(yīng)更廣闊的設(shè)計(jì)應(yīng)用。然而PLD雙雄當(dāng)前均未詳細(xì)透露各自28nm技術(shù)的產(chǎn)品規(guī)劃,估計(jì)要等到今年Q3方可完全揭曉。

殊途同歸的是,Altera和Xilinx都強(qiáng)調(diào)在28nm技術(shù)上的部分可重新配置功能,即FPGA器件無(wú)需斷電就可以通過(guò)軟件對(duì)其內(nèi)部邏輯進(jìn)行部分重置。不同的是,Xilinx宣稱(chēng)其在該功能的支持上更有經(jīng)驗(yàn),并革命性地統(tǒng)一Virtex和Spartan器件的內(nèi)部邏輯和I/O架構(gòu)來(lái)提供靈活的設(shè)計(jì)選擇;而Altera的28nm器件特點(diǎn)則是再結(jié)合嵌入式HardCopy模塊和更高速的收發(fā)器來(lái)遞送更高的性能。

28nm器件代工方面,Altera依然只由其長(zhǎng)期戰(zhàn)略伙伴臺(tái)積電(TSMC)代工,而堅(jiān)持多代工策略的Xilinx除選擇已是65nm代工伙伴的三星外,也轉(zhuǎn)而投入TSMC的懷抱。據(jù)悉,臺(tái)積電(TSMC)已經(jīng)準(zhǔn)備好在年內(nèi)試產(chǎn)高k金屬柵28nm器件。本刊同時(shí)認(rèn)為,和代工廠的博弈將會(huì)是決定FPGA雙雄獲取28nm市場(chǎng)競(jìng)爭(zhēng)籌碼多少的一個(gè)重要因素,比如在量產(chǎn)時(shí)間、產(chǎn)能支持等各方面。誠(chéng)然,激烈的市場(chǎng)競(jìng)爭(zhēng)是推動(dòng)28nm FPGA乃至加速PLD產(chǎn)業(yè)發(fā)展的源泉,而創(chuàng)新的28nm FPGA器件的推出,對(duì)用戶(hù)來(lái)說(shuō)無(wú)論如何都是好事一件,而不管哪個(gè)供應(yīng)商在最終的市場(chǎng)上表現(xiàn)更勝對(duì)方一籌。

能賦予設(shè)計(jì)更具靈活性的特點(diǎn)使市場(chǎng)對(duì)FPGA的需求也呈現(xiàn)多樣化。區(qū)別于SRAM FPGA在高端DSP和網(wǎng)絡(luò)處理應(yīng)用上的成就,另一PLD供應(yīng)商Actel就決意以基于Flash技術(shù)的低功耗FPGA進(jìn)行差異化競(jìng)爭(zhēng)。Actel亞太區(qū)總經(jīng)理賴(lài)炫州對(duì)《電子工程專(zhuān)輯》表示,Actel的策略是憑借混合信號(hào)FPGA創(chuàng)建屬于Actel自己的市場(chǎng)。他認(rèn)為,Actel最新推出集成ARM Cortex-M3硬核和可編程模擬模塊的SmartFusion FPGA,標(biāo)志著首款完全可編程的SoC的誕生。在其目標(biāo)應(yīng)用領(lǐng)域里,其相比MCU+ASSP的方案組合具有更高的集成度和設(shè)計(jì)靈活性,而對(duì)于基于CMOS工藝的SRAM FPGA而言,基于Flash工藝的SmartFusion擁有高壓模擬電路和數(shù)字電路共存的優(yōu)勢(shì)。賴(lài)炫州介紹,F(xiàn)lash FPGA需要高電壓燒錄,容易集成模擬資源,而SRAM FPGA在高電壓集成方面比較有挑戰(zhàn)性,一般來(lái)說(shuō),3.3V以上的信號(hào)難以集成到SRAM FPGA上。

SmartFusion的創(chuàng)新來(lái)自其嵌入了完整的微控制器子系統(tǒng),也是與前代集成軟核的Fusion產(chǎn)品的區(qū)別所在。可編程模擬方面,其主要具有幾個(gè)12位SAR ADC和Sigma-Delta DAC可選擇。而軟件支持方面,和大多數(shù)嵌入式開(kāi)發(fā)套件的內(nèi)容差不多,但其微控制器子系統(tǒng)的配置工具的確是一個(gè)亮點(diǎn),設(shè)計(jì)人員只需勾選相應(yīng)的外設(shè)和I/O與輸入硬件配置即可,而可編程模擬元件也可通過(guò)改工具進(jìn)行配置。

賴(lài)炫州強(qiáng)調(diào),在SmartFusion推出不久所擁有的十多個(gè)客戶(hù)來(lái)看,選擇Actel FPGA的關(guān)鍵還是其特有的保密性特點(diǎn)。由于Actel Flash FPGA是one die集成,外掛接口較少,加上多層次的保護(hù)措施,能有效防止創(chuàng)新的或差異化設(shè)計(jì)被競(jìng)爭(zhēng)對(duì)手抄襲、克隆,甚至被代工廠商過(guò)量生產(chǎn)。

]]>如果能在FPGA內(nèi)部嵌入具有外部測(cè)試設(shè)備功能的邏輯測(cè)試模塊,那么以上問(wèn)題就可以一一解決。SignalTapII就是這樣一種嵌入式邏輯分析器(embedded logicanaIyzer),簡(jiǎn)稱(chēng)為SignalTapII ELA。它是QuartusII軟件中集成的內(nèi)部邏輯分析軟件,使用它可以實(shí)時(shí)觀察內(nèi)部信號(hào)波形,方便用戶(hù)查找設(shè)計(jì)的缺陷。

1 SignalTapII ELA的原理

SignalTapII ELA是Quartus軟件中第二代系統(tǒng)級(jí)調(diào)試工具。將SignalTapII ELA代碼和系統(tǒng)邏輯代碼組合交由QuartusII編譯、綜合、布局布線(xiàn),生成sol文件中內(nèi)含SignalTapII ELA,把sof文件配置到FPGA內(nèi)。FPGA運(yùn)行時(shí),一旦滿(mǎn)足待測(cè)信號(hào)的觸發(fā)條件,SignalTapII ELA就立即啟動(dòng),按照采樣時(shí)鐘的頻率捕獲待測(cè)信號(hào)數(shù)據(jù)并暫存于FPGA片內(nèi)的RAM中,采樣數(shù)據(jù)不斷刷新片內(nèi)存儲(chǔ)器,最后通過(guò)JTAG口將捕獲的信號(hào)從片內(nèi)RAM傳至Quartus II實(shí)時(shí)顯示。SignalTapII ELA的原理流程如圖1所示。

實(shí)際工程中,加入SignalTapII ELA不會(huì)影響系統(tǒng)原有的邏輯功能。

2 SignalTapII ELA的配置

SignalTapII ELA基本配置過(guò)程如下:

①添加采樣時(shí)鐘。SignalTaplI ELA在時(shí)鐘的上升沿進(jìn)行采樣,可以使用設(shè)計(jì)系統(tǒng)中的任何信號(hào)作為采樣時(shí)鐘,根據(jù)Altera公司的建議最好使用同步系統(tǒng)全局時(shí)鐘作為采樣時(shí)鐘。但是在實(shí)際應(yīng)用中,多數(shù)使用獨(dú)立的采樣時(shí)鐘,這樣能采樣到被測(cè)系統(tǒng)中的慢速信號(hào),或與工作時(shí)鐘相關(guān)的信號(hào)。當(dāng)然采樣時(shí)鐘的頻率要大于被測(cè)信號(hào)的最高頻率,否則被測(cè)信號(hào)波形會(huì)有較大誤差。

②定義采樣深度。采樣深度決定了待測(cè)信號(hào)采樣存儲(chǔ)的大小,而可以采樣的深度是根據(jù)設(shè)計(jì)中剩余的RAM塊容量和待測(cè)信號(hào)的個(gè)數(shù)決定的。若待測(cè)信號(hào)較多,則在同樣I/O Bank個(gè)數(shù)情況下采樣深度較淺。待測(cè)信號(hào)個(gè)數(shù)的增減和采樣深度的深淺會(huì)直接改變RAM塊的占用情況,采樣深度的范圍為0~128 KB。

③定義RAM類(lèi)型。設(shè)置占用片內(nèi)何種RAM塊資源,隨著采樣深度的改變,RAM塊的數(shù)據(jù)線(xiàn)和地址線(xiàn)寬度可以分割成多種組合。例如:采樣深度是1 KB,RAM數(shù)據(jù)線(xiàn)、地址線(xiàn)可以分割成2×512或4×256等多種組合。依此類(lèi)推。

④定義觸發(fā)位置。Pre trigger position表示采樣到的數(shù)據(jù)12%為觸發(fā)前,88%為觸發(fā)后;Center trigger position表示采樣的數(shù)據(jù)處于觸發(fā)前后各一半;Post trigger position表示采樣到的數(shù)據(jù)88%為觸發(fā)前,12%為觸發(fā)后。

⑤觸發(fā)條件級(jí)數(shù)設(shè)置。SignalTapII ELA支持多觸發(fā)級(jí)的觸發(fā)方式,最多可支持10級(jí)觸發(fā),幫助濾除不相干的數(shù)據(jù),更快地找到需要的數(shù)據(jù)。若有多級(jí)觸發(fā)條件,首先分析第一級(jí)觸發(fā)條件。若第一級(jí)為T(mén)RUE,則轉(zhuǎn)到分析第二級(jí)是否滿(mǎn)足,直到分析完所有觸發(fā)條件均為T(mén)RUE才最終觸發(fā)時(shí)鐘采樣數(shù)據(jù)。

⑥觸發(fā)條件。設(shè)定約束性的觸發(fā)條件。可以允許單個(gè)信號(hào)的獨(dú)立觸發(fā)條件Basic,直接采用單個(gè)外部或設(shè)計(jì)模塊內(nèi)部的信號(hào);也可以允許多個(gè)節(jié)點(diǎn)信號(hào)的組合觸發(fā)條件Advanced,構(gòu)成觸發(fā)函數(shù)的觸發(fā)條件方程。例如:使能信號(hào)ENA與4位輸出信號(hào)Q相與后觸發(fā),觸發(fā)條件=ENA&(Q=15)。

]]>

隨著電子元件的性能和集成度不斷提高而價(jià)格卻不斷降低,電子控制單元的發(fā)展正一日千里。隨著各種技術(shù)和應(yīng)用大量涌現(xiàn),從家電領(lǐng)域到工業(yè)自動(dòng)化生產(chǎn)線(xiàn),大家關(guān)注的重點(diǎn)還是在增加設(shè)計(jì)和提高電源效率的同時(shí)能減少設(shè)計(jì)、開(kāi)發(fā)和整體的系統(tǒng)成本。

與此同時(shí),運(yùn)動(dòng)控制應(yīng)用的復(fù)雜程度也越來(lái)越高,已從簡(jiǎn)單的開(kāi)/關(guān)型控制向在高度集成環(huán)境中具備精確控制的可變速應(yīng)用發(fā)展。無(wú)論是交流、直流、有刷和無(wú)刷電機(jī)的各種控制電路主要由三部分構(gòu)成:人機(jī)界面、微控制器(MCU) 和控制邏輯。對(duì)于閉環(huán)運(yùn)動(dòng)控制,傳感器接口是外加的一個(gè)元件(圖1)。將運(yùn)動(dòng)控制邏輯納入數(shù)字領(lǐng)域可以實(shí)現(xiàn)分布式環(huán)境控制。運(yùn)動(dòng)控制電子和分布網(wǎng)絡(luò)的配合可在車(chē)間實(shí)現(xiàn)多種新功能,包括遠(yuǎn)程管理;適應(yīng)不斷變化的協(xié)議;性能監(jiān)視;以及按期進(jìn)行維護(hù)。

舉例說(shuō),當(dāng)今汽車(chē)制造業(yè)廣泛使用由步進(jìn)電機(jī)驅(qū)動(dòng)的機(jī)械手。機(jī)械手系統(tǒng)使得分布式控制更為復(fù)雜,而不同的機(jī)械手要同時(shí)在幾個(gè)車(chē)輛上安裝不同的零件。系統(tǒng)設(shè)計(jì)人員主要的挑戰(zhàn)之一是要通過(guò)局域網(wǎng)

絡(luò)實(shí)現(xiàn)各個(gè)機(jī)械手和其他自動(dòng)化設(shè)備的同步。更復(fù)雜的是,遠(yuǎn)程管理功能(如監(jiān)視、數(shù)據(jù)共享和遠(yuǎn)程配置) 對(duì)復(fù)雜的中央控制拓?fù)浣Y(jié)構(gòu)往往非常關(guān)鍵,也就是說(shuō),必需有一個(gè)有效的分布控制機(jī)制。

隨著半導(dǎo)體工藝和集成度的提高,現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA) 已成為許多電子運(yùn)動(dòng)控制應(yīng)用的重要替代平臺(tái)。FPGA的發(fā)展迅猛,在許多應(yīng)用領(lǐng)域中替代了特定用途集成電路(ASIC)。非易失性FPGA是具成本效益的ASIC替代方案,不存在采用ASIC時(shí)涉及開(kāi)發(fā)成本高和開(kāi)發(fā)時(shí)間長(zhǎng)的問(wèn)題。而且,利用FPGA替代固定的邏輯,設(shè)計(jì)人員無(wú)論在設(shè)計(jì)階段還是在應(yīng)用現(xiàn)場(chǎng),都可以高效、可靠地實(shí)現(xiàn)產(chǎn)品升級(jí)及定制功能。

以Flash 為基礎(chǔ)的混合信號(hào)FPGA (如Actel Fusion PSC) 能在單芯片上實(shí)現(xiàn)前所未有的集成度。因此,這類(lèi)器件可替代多個(gè)分立元件,能使成本和占用板卡空間減少最少50%,同時(shí)又能維持系統(tǒng)的可靠性(圖2)。而且,混合信號(hào)器件上集成的Flash 內(nèi)存可以讓設(shè)計(jì)人員存儲(chǔ)設(shè)計(jì)文檔,不象那些以SRAM為基礎(chǔ)的FPGA需要另外配置PROM。此外,與其他可重編程FPGA解決方案一樣,可配置和靈活的混合信號(hào)FPGA器件可以在開(kāi)發(fā)過(guò)程中甚至應(yīng)用之后,輕易進(jìn)行設(shè)計(jì)變更。

眾所周知,F(xiàn)PGA能通過(guò)并行處理加快數(shù)學(xué)運(yùn)算,使它成為實(shí)現(xiàn)電機(jī)控制邏輯的理想選擇。FPGA能執(zhí)行更嚴(yán)格的控制環(huán),因此提供更佳的控制和更少的波動(dòng)和噪聲。設(shè)計(jì)人員還能在集成了Flash 內(nèi)存的混合信號(hào)FPGA中集成軟處理器核,從片上存儲(chǔ)器直接運(yùn)行,從而緊密地配合控制邏輯和中斷驅(qū)動(dòng)程序的需要。由于設(shè)計(jì)中的邏輯門(mén)數(shù)量和類(lèi)型及控制邏輯的功能因應(yīng)用而有所不同,即基于性能要求而定;因此,可編程邏輯往往最適合于實(shí)現(xiàn)各種用戶(hù)接口和數(shù)字控制邏輯,包括網(wǎng)絡(luò)和外設(shè)接口、脈沖寬度調(diào)制(PWM),以及正交編碼器接口和傳感器輸入;這對(duì)當(dāng)今的運(yùn)動(dòng)控制系統(tǒng)都非常重要。

網(wǎng)絡(luò)和外設(shè)接口

在運(yùn)動(dòng)控制系統(tǒng)中,網(wǎng)絡(luò)和外設(shè)接口可讓用戶(hù)發(fā)出指令對(duì)邏輯電路進(jìn)行初始化、配置和控制,并且遠(yuǎn)程管理控制系統(tǒng)。根據(jù)功能和拓?fù)浣Y(jié)構(gòu)的不同,每個(gè)運(yùn)動(dòng)控制系統(tǒng)的網(wǎng)絡(luò)和外設(shè)接口都可能會(huì)采取獨(dú)特的實(shí)現(xiàn)方式,但有一點(diǎn)共同的是,都會(huì)利用接口來(lái)提高系統(tǒng)的可訪問(wèn)性。

目前已經(jīng)有各種各樣的工業(yè)標(biāo)準(zhǔn)接口,如用于本地訪問(wèn)的通用串行總線(xiàn)(USB)、基于RS232的串口和控制器局域網(wǎng)(CAN) 接口,以及基于TCP/IP網(wǎng)絡(luò)協(xié)議的10/100以太網(wǎng)。在苛刻的環(huán)境下,如汽車(chē)制造車(chē)間,可能還需要無(wú)線(xiàn)網(wǎng)絡(luò)接口。這種接口可在制造車(chē)間內(nèi)實(shí)現(xiàn)系統(tǒng)同步、數(shù)據(jù)共享、狀態(tài)監(jiān)視和故障報(bào)警。此外,基于TCP/IP的網(wǎng)絡(luò)接口則用于延長(zhǎng)由任何距離遠(yuǎn)程訪問(wèn)中央制造控制設(shè)施的能力。

在許多情況下,工業(yè)自動(dòng)化應(yīng)用都需要特殊的控制算法和裝置來(lái)完成特殊的任務(wù)。為實(shí)現(xiàn)這些標(biāo)準(zhǔn)接口無(wú)法提供的功能,需要考慮采用專(zhuān)門(mén)的接口。為了充分發(fā)揮某個(gè)分布控制系統(tǒng)的潛力,標(biāo)準(zhǔn)接口或?qū)iT(mén)的網(wǎng)絡(luò)協(xié)議都必須加到板卡級(jí)中,或嵌入到可編程邏輯內(nèi)。而FPGA是將所有接口集成在一起的最佳平臺(tái)。特別是,當(dāng)今的混合信號(hào)FPGA器件具有模擬前端,能支持種類(lèi)眾多的用戶(hù)輸入,以及實(shí)現(xiàn)運(yùn)動(dòng)控制所需的電壓、電流和溫度監(jiān)視功能。

脈沖寬度調(diào)制(PWM)

PWM邏輯并不是所有運(yùn)動(dòng)控制應(yīng)用都適用的方案。由于不同電機(jī)的繞組圈數(shù)、額定電壓/電流、扭矩曲線(xiàn)和其他參數(shù)的差異很大,因此每種PWM系統(tǒng)都需要對(duì)這些差異加以考慮。在PWM控制的系統(tǒng)中,施加電壓的順序決定電機(jī)的轉(zhuǎn)動(dòng)方向。在給定繞組電感下,占空比(或者說(shuō)脈沖頻率和脈沖串長(zhǎng)度) 決定了電機(jī)的峰值電流和磁通量(即其扭矩大小)。機(jī)械動(dòng)量和繞組電感(部分由繞組圈數(shù)所決定) 會(huì)使PWM電壓變得平滑。通過(guò)控制驅(qū)動(dòng)電路的加壓順序、頻率和占空比,PWM 系統(tǒng)就可控制方向、速度和平均扭矩。利用FPGA 器件,設(shè)計(jì)人員可以構(gòu)建最適合系統(tǒng)要求的PWM方案,而不必非得采用傳統(tǒng)的MCU/DSP方案來(lái)實(shí)現(xiàn)。

正交編碼器接口(QEI)

大多數(shù)高精度電機(jī)(如用于機(jī)械手的伺服步進(jìn)電機(jī)) 都支持正交編碼器接口。控制系統(tǒng)必需提供正交編碼器接口邏輯來(lái)精確電機(jī)速度、位置和加速。當(dāng)然,采用可編程邏輯技術(shù)便可在各種模式下取決于運(yùn)動(dòng)控制系統(tǒng)中采用的電機(jī)特性,精確并動(dòng)態(tài)地調(diào)節(jié)速度。

傳感器輸入

對(duì)于閉環(huán)運(yùn)動(dòng)控制系統(tǒng),需要有轉(zhuǎn)子位置和/或轉(zhuǎn)數(shù)輸入。這些輸入可以是內(nèi)置的霍耳效應(yīng)傳感器或外接的光學(xué)位置編碼器、同步解析器或磁感應(yīng)傳感器。利用集成的模擬前端,混合信號(hào)FPGA將提供更加集成的解決方案,能夠減少部件數(shù)、降低系統(tǒng)成本和提高可靠性。

可靠性和系統(tǒng)正常運(yùn)行時(shí)間

對(duì)于今天的電子系統(tǒng),高性能、低集成成本和快速診斷能力非常關(guān)鍵。診斷和預(yù)報(bào),即確定故障類(lèi)型并作出預(yù)報(bào)的功能,在系統(tǒng)管理中的重要性越來(lái)越高。讀取帶有時(shí)間標(biāo)記系統(tǒng)參數(shù)的各種板卡運(yùn)行的功能或事后分析故障的功能對(duì)于系統(tǒng)開(kāi)發(fā)是無(wú)價(jià)之寶。同樣地,能構(gòu)建出一個(gè)"黑匣子"將為查找故障類(lèi)型和設(shè)計(jì)缺陷節(jié)省寶貴的時(shí)間和精力。

混合信號(hào)FPGA的片上Flash 內(nèi)存可保存關(guān)鍵的系統(tǒng)參數(shù),并對(duì)其作時(shí)間標(biāo)記,如電源線(xiàn)路電流消耗、器件溫度和電壓波動(dòng)等。這些數(shù)據(jù)不僅可用于事后故障分析,而且還可讓創(chuàng)新的設(shè)計(jì)人員用于運(yùn)行中的系統(tǒng)趨勢(shì)分析。例如,設(shè)計(jì)人員可以測(cè)量(當(dāng)輸入某一電壓時(shí)) 繞組的電流和電機(jī)的振動(dòng),以確定什么情況下按計(jì)劃的方式關(guān)閉設(shè)備。在工業(yè)應(yīng)用中,從解決故障問(wèn)題所需的成本以及設(shè)備關(guān)閉所造成的利潤(rùn)損失來(lái)考慮,按計(jì)劃的方案關(guān)閉設(shè)備比意外關(guān)閉的費(fèi)用要少得多。混合信號(hào)FPGA可讓設(shè)計(jì)人員通過(guò)分析某一特定參數(shù)如何改變板卡的壽命,在故障發(fā)生前作出預(yù)報(bào),從而最大限度地提高機(jī)器利用率,延長(zhǎng)系統(tǒng)的正常運(yùn)行時(shí)間,并降低可能造成重大損失的系統(tǒng)崩潰風(fēng)險(xiǎn)。

電機(jī)的應(yīng)用范圍很廣,而且許多應(yīng)用都正在由機(jī)電設(shè)計(jì)轉(zhuǎn)向電子設(shè)計(jì)。計(jì)算機(jī)和功率電子器件的成本一直是推廣電子電機(jī)控制廣泛應(yīng)用的障礙之一。隨著半導(dǎo)體工藝和功能集成技術(shù)的進(jìn)步,這個(gè)障礙正在慢慢消失。而且,由于今天采用固定功能實(shí)現(xiàn)方式的成本仍然很高,常常需要不同的部件和在各個(gè)設(shè)計(jì)反復(fù)環(huán)節(jié)作板卡級(jí)變更,F(xiàn)PGA遂成為了許多運(yùn)動(dòng)控制應(yīng)用的替代解決方案。

理想的運(yùn)動(dòng)控制設(shè)計(jì)往往需要將一些可協(xié)同操作的部件放在一起,使它們能在運(yùn)行中和諧配合。而混合信號(hào)FPGA解決方案的功能集成度非常高,正好能滿(mǎn)足這種需求,可以大幅減少部件數(shù)目、板卡空間和整體系統(tǒng)成本,從而增加系統(tǒng)的可靠性和正常運(yùn)行時(shí)間。

相似的,您現(xiàn)在創(chuàng)建的測(cè)量與控制系統(tǒng)也可以同時(shí)進(jìn)行多項(xiàng)任務(wù)。計(jì)算領(lǐng)域的工程創(chuàng)新引進(jìn)了許多建立更高效并行系統(tǒng)所需的關(guān)鍵技術(shù):多核處理器、現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)和無(wú)線(xiàn)通信。使用這些傳統(tǒng)工具利用這些關(guān)鍵技術(shù)并不十分容易;但是,如果在應(yīng)用中使用這些技術(shù),就可以獲得性能更高的系統(tǒng),提高測(cè)量與自動(dòng)化系統(tǒng)的吞吐量,降低成本。LabVIEW的最新版本8.6為您提供了使用下一代并行技術(shù)所需的工具,從多核處理器到高性能FPGA直至無(wú)線(xiàn)設(shè)備。

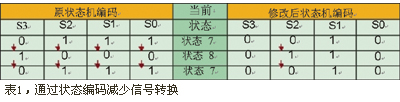

圖1:NI機(jī)器視覺(jué)開(kāi)發(fā)模塊的例如圖像卷積函數(shù)等多個(gè)圖像處理函數(shù)現(xiàn)在能夠自動(dòng)分配到多個(gè)核心進(jìn)行處理。

在桌面上進(jìn)行多核超級(jí)計(jì)算

在世界最頂級(jí)的500臺(tái)超級(jí)計(jì)算機(jī)(www.top500.org)的最新排名中,有77%使用了多核處理器簇,而在2007年這個(gè)數(shù)字只有22%。這些超級(jí)計(jì)算機(jī)和您現(xiàn)在PC中使用的多核處理器是相同的。當(dāng)然,要充分利用這些超級(jí)計(jì)算機(jī)需要編寫(xiě)專(zhuān)用的軟件。幸運(yùn)的是,LabVIEW的設(shè)計(jì)就已經(jīng)考慮了并行處理,對(duì)多任務(wù)處理的支持已經(jīng)長(zhǎng)達(dá)10多年。

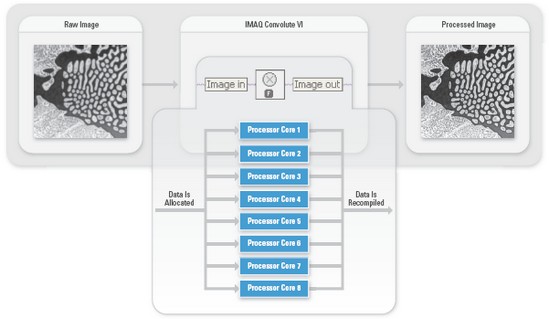

圖2:LabVIEW 8.6為FPGA編程提供了強(qiáng)大的算法工程平臺(tái),包含了交互式用戶(hù)界面、大型分析庫(kù)以及到實(shí)時(shí)硬件原型上的快速移植。

LabVIEW 8.6是基于現(xiàn)有的多核兼容性而編寫(xiě)的,大大提高了利用多核處理所能夠獲得的性能。在LabVIEW 8.6中超過(guò)1200個(gè)數(shù)學(xué)和信號(hào)處理庫(kù)中的函數(shù)已經(jīng)為多核系統(tǒng)進(jìn)行了優(yōu)化;此外,新型的高級(jí)緩存連續(xù)技術(shù)能夠進(jìn)一步提高性能。這樣使得對(duì)CPU核心的使用更為高效。舉例來(lái)說(shuō),相對(duì)于單核系統(tǒng)而言,一個(gè)運(yùn)行在八核系統(tǒng)上的基準(zhǔn)測(cè)試程序運(yùn)行快了6.6倍。LabVIEW控制設(shè)計(jì)與仿真模塊也使用了多核處理器,執(zhí)行并行動(dòng)態(tài)系統(tǒng)仿真模塊快了5倍。NI機(jī)器視覺(jué)開(kāi)發(fā)模塊中的多個(gè)圖像處理函數(shù)已經(jīng)為自動(dòng)將任務(wù)平分到多個(gè)核心中進(jìn)行了優(yōu)化。例如,圖像卷積函數(shù)的基準(zhǔn)測(cè)試在雙核系統(tǒng)上運(yùn)行快了高達(dá)15倍(見(jiàn)圖1)。這些新型特性為您的測(cè)量或控制系統(tǒng)提供了超級(jí)計(jì)算機(jī)級(jí)別的性能。

降低FPGA開(kāi)發(fā)時(shí)間

FPGA可能是現(xiàn)在并行能力最高的可編程計(jì)算硬件,為測(cè)量和控制系統(tǒng)提供了前所未有的性能和可靠性。但是,由于FPGA的開(kāi)發(fā)困難重重,許多工程師不太愿意涉足FPGA編程。甚至算法設(shè)計(jì)專(zhuān)家在進(jìn)行定點(diǎn)實(shí)現(xiàn)的工作也覺(jué)得十分困難。LabVIEW提供了強(qiáng)大的算法工程平臺(tái),使用交互式用戶(hù)界面、大型分析庫(kù)和與實(shí)時(shí)硬件原型的快速移植特性,滿(mǎn)足了這些挑戰(zhàn)的需求。LabVIEW 8.6擴(kuò)展了這些課題,解決了下面列出的最為常見(jiàn)的FPGA挑戰(zhàn)。

1、使用傳統(tǒng)的FPGA開(kāi)發(fā)軟件需要數(shù)字設(shè)計(jì)的專(zhuān)業(yè)知識(shí)——使用LabVIEW直觀的數(shù)據(jù)流模型,您可以使用圖形化LabVIEW FPGA模塊,對(duì)FPGA進(jìn)行編程,而不必學(xué)習(xí)硬件描述語(yǔ)言(HDL)的復(fù)雜內(nèi)容。

2、FPGA代碼在執(zhí)行之前可能需要很長(zhǎng)的編譯周期——LabVIEW 8.6大大增強(qiáng)了FPGA開(kāi)發(fā)和調(diào)試特性,您可以在無(wú)需編譯的情況下,在開(kāi)發(fā)計(jì)算機(jī)上對(duì)FPGA和主機(jī)接口代碼進(jìn)行仿真。此外,現(xiàn)在您可以在無(wú)需修改FPGA代碼的情況下,通過(guò)仿真I/O信號(hào)為FPGA邏輯建立測(cè)試工作臺(tái),在編譯之前對(duì)設(shè)計(jì)進(jìn)行驗(yàn)證。

如果您使用NI CompactRIO硬件,就可以利用LabVIEW 8.6中全新的CompactRIO掃描模式特性,無(wú)需對(duì)FPGA進(jìn)行編程,訪問(wèn)實(shí)時(shí)處理器的I/O。有了這個(gè)全新選項(xiàng),在您的應(yīng)用程序需要更高性能或是自定義行為時(shí),可以選擇“全面開(kāi)啟”FPGA。

3、將算法從軟件原型移植到硬件實(shí)現(xiàn)中十分困難——由于LabVIEW可以運(yùn)行在臺(tái)式機(jī)平臺(tái)和FPGA上,相對(duì)于使用傳統(tǒng)工具需要重寫(xiě)算法而言,從臺(tái)式機(jī)到硬件的過(guò)渡十分平滑。LabVIEW 8.6中FPGA上的新增定點(diǎn)數(shù)據(jù)類(lèi)型支持和例如快速傅立葉變換(FFT)函數(shù)等高級(jí)分析知識(shí)產(chǎn)權(quán)(IP)使得這種過(guò)渡更加順利。

4、使用最新的FPGA硬件更新設(shè)計(jì)需要耗費(fèi)時(shí)間和資金——LabVIEW通過(guò)利用硬件抽象保護(hù)了您的開(kāi)發(fā)投資,因此您可以使用全新硬件平臺(tái),例如基于Xilinx Virtex-5 FPGA的NI R系列設(shè)備和NI單板RIO板卡專(zhuān)用可重復(fù)配置I/O(RIO)平臺(tái),而無(wú)需對(duì)LabVIEW FPGA代碼進(jìn)行修改。

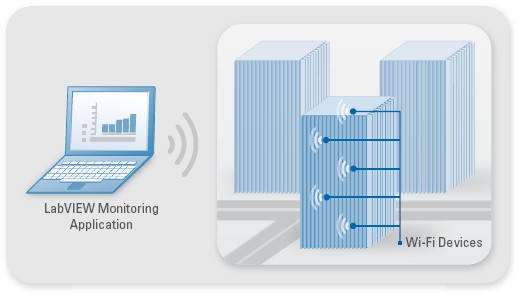

簡(jiǎn)化Wi-Fi測(cè)量系統(tǒng)的實(shí)現(xiàn)

LabVIEW除了簡(jiǎn)化了在多核處理器和FPGA上的并行代碼開(kāi)發(fā)之外,還通過(guò)為新型NI Wi-Fi數(shù)據(jù)采集(DAQ)設(shè)備提供支持,簡(jiǎn)化了并行分布式測(cè)量的開(kāi)發(fā)和部署。盡管很久之前LabVIEW就已經(jīng)為一系列插入式和有線(xiàn)總線(xiàn)的數(shù)據(jù)采集提供了支持,包括PCI、PXI、USB、LAN和GPIB,但是在數(shù)據(jù)采集應(yīng)用中無(wú)線(xiàn)技術(shù)的引進(jìn)卻慢了很多。這主要是因?yàn)閷?duì)可靠、安全、高性能無(wú)線(xiàn)系統(tǒng)的編程和部署相對(duì)更為復(fù)雜。隨著Wi-Fi(IEEE 802.11)在IT領(lǐng)域中普及以來(lái),性能、可靠性和安全性已經(jīng)大大提高了這個(gè)技術(shù)能夠適用于包括數(shù)據(jù)采集在內(nèi)的關(guān)鍵任務(wù)的可行性。

對(duì)基于Wi-Fi的LabVIEW配置和數(shù)據(jù)采集步驟和對(duì)本地插入式USB設(shè)備的信號(hào)采集是相似的。兩者都使用相同的LabVIEW應(yīng)用程序接口(API)連接NI-DAQmx驅(qū)動(dòng)程序,從而避免了在將Wi-Fi設(shè)備加入到現(xiàn)有有線(xiàn)或插入式NI數(shù)據(jù)采集系統(tǒng)時(shí)所需的代碼修改。在LabVIEW中進(jìn)行編程的時(shí)候,您可以使用NI數(shù)據(jù)采集助手,這是一個(gè)基于配置的向?qū)В軌驇椭x測(cè)量,快速方便地通過(guò)Wi-Fi采集數(shù)據(jù)。LabVIEW 8.6中的數(shù)據(jù)采集助手和NI-DAQmx API使得將您的Wi-Fi系統(tǒng)從幾十個(gè)擴(kuò)展到上百個(gè)設(shè)備變得十分容易。現(xiàn)在您可以將LabVIEW 8.6和新型NI Wi-Fi數(shù)據(jù)采集驅(qū)動(dòng)程序用于以下應(yīng)用領(lǐng)域:

1、用于預(yù)測(cè)維護(hù)的機(jī)器監(jiān)視——機(jī)器狀態(tài)監(jiān)視可以預(yù)防意外事故、優(yōu)化機(jī)器性能,并且降低修理時(shí)間和維護(hù)成本。使用LabVIEW和Wi-Fi振動(dòng)測(cè)量,可以大大減少與機(jī)器監(jiān)視相關(guān)的安裝和布線(xiàn)成本。Wi-Fi數(shù)據(jù)采集還簡(jiǎn)化了筆記本電腦和基于PC的移動(dòng)現(xiàn)場(chǎng)診斷系統(tǒng)的建立。

2、結(jié)構(gòu)狀態(tài)的診斷監(jiān)視——結(jié)構(gòu)狀態(tài)監(jiān)視包括通過(guò)負(fù)載、壓力和張力等主要指標(biāo)對(duì)建筑和橋梁的性能進(jìn)行評(píng)估。由于這些結(jié)構(gòu)尺寸較大,使用有線(xiàn)解決方案成本高昂,并且難于實(shí)現(xiàn)。對(duì)于這些及其他動(dòng)態(tài)結(jié)構(gòu)測(cè)試應(yīng)用而言,高帶寬的全新NI Wi-Fi數(shù)據(jù)采集設(shè)備是使用LabVIEW在線(xiàn)分析,進(jìn)行振動(dòng)和張力測(cè)量連續(xù)數(shù)據(jù)流傳送的理想選擇。

3、環(huán)境質(zhì)量監(jiān)視——環(huán)境監(jiān)視的范圍包括土壤、水和空氣的完整度直至與溫度和濕度調(diào)節(jié)相關(guān)的服務(wù)器與易損品等重要資產(chǎn)的室內(nèi)儲(chǔ)藏。使用LabVIEW和Wi-Fi熱電偶和電壓測(cè)量,建立安裝與支持簡(jiǎn)單的無(wú)線(xiàn)遠(yuǎn)程監(jiān)督解決方案。

圖3:您可以在多種應(yīng)用中將新型Wi-Fi數(shù)據(jù)采集設(shè)備與LabVIEW一起使用,其中包括機(jī)器、診斷與環(huán)境監(jiān)視。

LabVIEW 8.6中的其他新特性

除了繼續(xù)引進(jìn)多核處理器、FPGA和Wi-Fi測(cè)量等最新并行技術(shù)之外,LabVIEW 8.6還包括了為長(zhǎng)期老用戶(hù)專(zhuān)門(mén)設(shè)計(jì)的新增特性和重要改進(jìn)。一個(gè)十分顯著的改變是通過(guò)LabVIEW平臺(tái)DVD套件所帶來(lái)的更好的用戶(hù)體驗(yàn),它大大簡(jiǎn)化了LabVIEW開(kāi)發(fā)系統(tǒng)、附加模塊和工具包以及NI兼容設(shè)備驅(qū)動(dòng)程序的安裝。在單一的對(duì)話(huà)框中,您可以安裝分布在多張DVD上的軟件,并且盡可能少地更換媒介。您還可以對(duì)DVD上所包含的您暫時(shí)并不擁有的軟件進(jìn)行30天的評(píng)估。

LabVIEW 8.6還包括了新增開(kāi)發(fā)特性,可以提高工作效率,其中包括全新的程序框圖整理工具,只需要單擊鼠標(biāo),就可以按照LabVIEW風(fēng)格指南中所給出的編程建議對(duì)程序框圖進(jìn)行大小改變和重新排列。我們知道LabVIEW選板隨著LabVIEW平臺(tái)的發(fā)展,變得越來(lái)越復(fù)雜,LabVIEW 8.6也引進(jìn)了快速放置功能,您可以使用可預(yù)測(cè)方式進(jìn)行選擇,對(duì)前面板和程序框圖對(duì)象進(jìn)行查找和放置。

世界是并行的,工程師和科學(xué)家必須能夠基于可響應(yīng)的軟件,開(kāi)發(fā)測(cè)量與自動(dòng)化系統(tǒng)。LabVIEW 8.6可以充分利用多核處理器、FPGA以及Wi-Fi數(shù)據(jù)采集設(shè)備,它提供了由其自身圖形化編程平臺(tái)所帶來(lái)的相同優(yōu)點(diǎn)——無(wú)論何如復(fù)雜都可以利用最新PC技術(shù)的能力。

Michael Neal是一位LabVIEW產(chǎn)品經(jīng)理。他獲取了德克薩斯大學(xué)奧斯汀分校的結(jié)構(gòu)工程學(xué)士學(xué)位和生物醫(yī)學(xué)工程碩士學(xué)位。

Gerardo Garcia是一位LabVIEW實(shí)時(shí)與工業(yè)控制的部門(mén)經(jīng)理。他獲得了德州農(nóng)機(jī)大學(xué)的電子工程學(xué)士學(xué)位。

]]>

1 概述

--- 隨著FPGA容量的增大,F(xiàn)PGA的設(shè)計(jì)日益復(fù)雜,設(shè)計(jì)調(diào)試成為一個(gè)非常繁重的任務(wù)。為了使得設(shè)計(jì)盡快投入市場(chǎng),設(shè)計(jì)人員需要一種簡(jiǎn)易有效的測(cè)試工具,以盡可能的縮短測(cè)試時(shí)間。傳統(tǒng)的邏輯分析儀在測(cè)試復(fù)雜的FPGA設(shè)計(jì)時(shí),將會(huì)面臨以下幾點(diǎn)問(wèn)題:1)缺少空余I/O引腳。設(shè)計(jì)中器件的選擇依據(jù)設(shè)計(jì)規(guī)模而定,通常所選器件的I/O引腳數(shù)目和設(shè)計(jì)的需求是恰好匹配的。2)I/O引腳難以引出。設(shè)計(jì)者為減小電路板的面積,大都采用細(xì)間距工藝技術(shù),在不改動(dòng)PCB板布線(xiàn)的情況下引出I/O引腳非常困難。3)外接邏輯分析儀有改動(dòng)FPGA設(shè)計(jì)中信號(hào)原來(lái)狀態(tài)的可能,因此難以確保信號(hào)的正確性。4)傳統(tǒng)的邏輯分析儀價(jià)格昂貴,將會(huì)加重設(shè)計(jì)方的經(jīng)濟(jì)負(fù)擔(dān)。

--- 伴隨著EDA工具的快速發(fā)展,一種新的調(diào)試工具Quartus II 中的SignalTap II 滿(mǎn)足了FPGA研發(fā)中硬件調(diào)試的需求,他具有無(wú)干擾、便于升級(jí)、使用簡(jiǎn)單、價(jià)格低廉等特點(diǎn)。本文將介紹SignalTap II邏輯分析儀的主要特點(diǎn)和使用流程,并以一個(gè)實(shí)例介紹該分析儀具體的操作方法和步驟。

2 SignalTap II的特點(diǎn)及使用

--- SignalTap II嵌入邏輯分析儀集成到Quartus II設(shè)計(jì)軟件中,能夠捕捉和顯示可編程單芯片系統(tǒng)(SOPC)設(shè)計(jì)中實(shí)時(shí)信號(hào)的狀態(tài),這樣研發(fā)者就能在整個(gè)設(shè)計(jì)過(guò)程中以系統(tǒng)級(jí)的速度觀察硬件和軟件的交互作用。他支持多達(dá)1024個(gè)通道,采樣深度高達(dá)128Kb,每個(gè)分析儀均有10級(jí)觸發(fā)輸入/輸出,從而增加了采樣的精度。SignalTap II為設(shè)計(jì)者提供了業(yè)界領(lǐng)先的SOPC設(shè)計(jì)的實(shí)時(shí)可視性,能夠大大減少驗(yàn)證過(guò)程中所花費(fèi)的時(shí)間。目前SignalTap II邏輯分析儀支持的器件系列包括:APEXT II, APEX20KE, APEX20KC, APEX20K, Cyclone, Excalibur, Mercury, Stratix GX, Stratix。

--- SignalTap II將邏輯分析模塊嵌入到FPGA中,如圖1所示。邏輯分析模塊對(duì)待測(cè)節(jié)點(diǎn)的數(shù)據(jù)進(jìn)行捕捉,數(shù)據(jù)通過(guò)JTAG接口從FPGA傳送到Quartus II軟件中顯示。使用SignalTap II無(wú)需額外的邏輯分析設(shè)備,只需將一根JTAG接口的下載電纜連接到要調(diào)試的FPGA器件。SignalTap II對(duì)FPGA的引腳和內(nèi)部的連線(xiàn)信號(hào)進(jìn)行捕捉后,將數(shù)據(jù)存儲(chǔ)在一定的RAM塊中。因此,需要用于捕捉的采樣時(shí)鐘信號(hào)和保存被測(cè)信號(hào)的一定點(diǎn)數(shù)的RAM塊。

--- 使用SignalTap II的一般流程是:設(shè)計(jì)人員在完成設(shè)計(jì)并編譯工程后,建立SignalTap II (.stp)文件并加入工程、設(shè)置STP文件、編譯并下載設(shè)計(jì)到FPGA、在Quartus II軟件中顯示被測(cè)信號(hào)的波形、在測(cè)試完畢后將該邏輯分析儀從項(xiàng)目中刪除。以下描述設(shè)置 SignalTap II 文件的基本流程:

--- 1.設(shè)置采樣時(shí)鐘。采樣時(shí)鐘決定了顯示信號(hào)波形的分辨率,他的頻率要大于被測(cè)信號(hào)的最高頻率,否則無(wú)法正確反映被測(cè)信號(hào)波形的變化。SignalTap II在時(shí)鐘上升沿將被測(cè)信號(hào)存儲(chǔ)到緩存。

--- 2.設(shè)置被測(cè)信號(hào)。能使用Node Finder 中的 SignalTap II 濾波器查找所有預(yù)綜合和布局布線(xiàn)后的SignalTap II 節(jié)點(diǎn),添加要觀察的信號(hào)。邏輯分析器不可測(cè)試的信號(hào)包括:邏輯單元的進(jìn)位信號(hào)、PLL的時(shí)鐘輸出、JTAG引腳信號(hào)、LVDS(低壓差分)信號(hào)。

--- 3.設(shè)置采樣深度、確定RAM的大小。SignalTap II所能顯示的被測(cè)信號(hào)波形的時(shí)間長(zhǎng)度為T(mén)x,計(jì)算公式如下:

--- Tx=N×Ts

--- N為緩存中存儲(chǔ)的采樣點(diǎn)數(shù),Ts為采樣時(shí)鐘的周期。

--- 4.設(shè)置buffer acquisition mode。buffer acquisition mode包括循環(huán)采樣存儲(chǔ)、連續(xù)存儲(chǔ)兩種模式。循環(huán)采樣存儲(chǔ)也就是分段存儲(chǔ),將整個(gè)緩存分成多個(gè)片段(segment),每當(dāng)觸發(fā)條件滿(mǎn)足時(shí)就捕捉一段數(shù)據(jù)。該功能能去掉無(wú)關(guān)的數(shù)據(jù),使采樣緩存的使用更加靈活。

--- 5.觸發(fā)級(jí)別。SignalTap II支持多觸發(fā)級(jí)的觸發(fā)方式,最多可支持10級(jí)觸發(fā)。

--- 6.觸發(fā)條件。能設(shè)定復(fù)雜的觸發(fā)條件用來(lái)捕捉相應(yīng)的數(shù)據(jù),以協(xié)助調(diào)試設(shè)計(jì)。當(dāng)觸發(fā)條件滿(mǎn)足時(shí),在signalTap時(shí)鐘的上升沿采樣被測(cè)信號(hào)。

--- 完成STP設(shè)置后,將STP文件同原有的設(shè)計(jì)下載到FPGA中,在Quartus II中SignalTap II窗口下查看邏輯分析儀捕捉結(jié)果。SignalTap II可將數(shù)據(jù)通過(guò)多余的I/O引腳輸出,以供外設(shè)的邏輯分析器使用;或輸出為csv、tbl、vcd、vwf文件格式以供第三方仿真工具使用。

3 實(shí)例分析

--- 本文以一個(gè)ADC0809器件的采樣控制器作為實(shí)例,具體說(shuō)明怎么用SignalTap II 來(lái)進(jìn)行FPGA設(shè)計(jì)的驗(yàn)證。使用Altera公司的器件Cyclone系列FPGA- EP1C12Q240C8,該器件支持SignalTap II 嵌入式邏輯分析儀的使用。

--- FPGA的設(shè)計(jì)結(jié)構(gòu)如圖2所示。數(shù)字倍頻器的倍頻輸出提供ADC控制器的采樣觸發(fā)脈沖。A/D轉(zhuǎn)換器ADC0809的操作時(shí)序見(jiàn)數(shù)據(jù)手冊(cè),根據(jù)其操作時(shí)序,ADC控制器來(lái)實(shí)現(xiàn)ADC0809的數(shù)據(jù)采集操作,采樣的時(shí)機(jī)由倍頻器來(lái)控制。控制器每控制完成一次采樣操作,則停止等待下一個(gè)觸發(fā)脈沖的到來(lái)。倍頻器每輸出一個(gè)低電平脈沖,ADC采樣控制器的狀態(tài)機(jī)進(jìn)行一次采樣操作。在倍頻器的觸發(fā)控制下,完成被測(cè)信號(hào)一個(gè)基波周期N個(gè)點(diǎn)的等間隔采樣,同時(shí)數(shù)字倍頻器跟蹤輸入信號(hào)的頻率的變化,盡可能地保持N個(gè)點(diǎn)的采樣寬度正好為被測(cè)信號(hào)一個(gè)周波的寬度。

--- 測(cè)試項(xiàng)目是基于FPGA的AD采樣控制器,他是用狀態(tài)機(jī)控制的周期性的重復(fù)事件,一次采樣操作完成后等待采樣脈沖、開(kāi)始下一次的采樣。針對(duì)待測(cè)項(xiàng)目的周期性,

--- 在STP文件中將buffer acquisition mode分別設(shè)為連續(xù)存儲(chǔ)和循環(huán)采樣存儲(chǔ)兩種模式進(jìn)行驗(yàn)證。連續(xù)存儲(chǔ)方式記錄采樣操作的連續(xù)過(guò)程,而在循環(huán)采樣存儲(chǔ)方式下SignalTap II記錄多次采樣時(shí)刻數(shù)據(jù)。

--- 按照上述SignalTap II的使用步驟,在編譯后的工程中添加STP文件,并對(duì)文件進(jìn)行設(shè)置,如圖3所示。如1處設(shè)置采樣時(shí)鐘ct[3],系統(tǒng)時(shí)鐘的16分頻。2處添加測(cè)試信號(hào),包括待測(cè)模塊輸出的AD采樣控制信號(hào)和狀態(tài)機(jī)的狀態(tài)等。3處是采樣深度的設(shè)置,設(shè)為512。在4處的設(shè)置確定了在clko時(shí)鐘的上升沿觸發(fā)邏輯分析儀。在連續(xù)存儲(chǔ)模式下設(shè)置buffer acquisition mode為Circular前觸發(fā)位置。在分段存儲(chǔ)模式下設(shè)置為Sigmented 512 1 bit segments,表示將存儲(chǔ)區(qū)劃分成512個(gè)段,每段1個(gè)位的存儲(chǔ)深度。存儲(chǔ)模式的設(shè)置如圖中6所示。另外,使用Mnemonic Table將狀態(tài)機(jī)的7個(gè)狀態(tài)標(biāo)示為直觀名稱(chēng)。

--- 首先將STP文件設(shè)置成連續(xù)存儲(chǔ)模式,并將該文件連同工程一起下載到FPGA中。在連續(xù)存儲(chǔ)模式下,SignalTap II在clko時(shí)鐘的上升沿連續(xù)采樣直到采樣點(diǎn)數(shù)達(dá)到512個(gè)。這樣,SignalTap II記錄了一次采樣過(guò)程的所有數(shù)據(jù),捕捉結(jié)果如圖4所示,從中能看到FPGA控制ADC0809轉(zhuǎn)換的時(shí)序波形。

--- 將圖3所示步驟6中的Buffer acquisition node改為Segmented方式,設(shè)其值為256 1 bit segments,并將修改后的STP文件連同工程重新下載到FPGA中。和單次觸發(fā)相同的是邏輯分析儀在ADC0809采樣時(shí)鐘上升沿時(shí)觸發(fā)邏輯分析儀,不同的是因?yàn)槊恳欢沃挥?bit的存儲(chǔ)深度,因此捕捉1位數(shù)據(jù)后邏輯分析儀停止,等待下一次滿(mǎn)足觸發(fā)信號(hào)再次啟動(dòng),一共啟動(dòng)256次。在波形顯示窗口,設(shè)顯示格式為L(zhǎng)ine Chart,這樣結(jié)果就直觀的顯示為連續(xù)的波形。分片采樣,可觀察同步采樣的結(jié)果,圖5是連續(xù)采樣256個(gè)點(diǎn)的結(jié)果波形。

4 結(jié)論

--- SignalTap II 嵌入式邏輯分析器,提供了芯片測(cè)試的一個(gè)非常好的途徑。通過(guò)SignalTap II 測(cè)試芯片無(wú)需外接專(zhuān)用儀器,他在器件內(nèi)部捕捉節(jié)點(diǎn)進(jìn)行分析和判斷系統(tǒng)故障。本文通過(guò)對(duì)Cyclone EP1C12器件的實(shí)驗(yàn)證實(shí)該測(cè)試手段大大提高系統(tǒng)的調(diào)試能力,具有非常好的效果。